-

高空电磁脉冲(HEMP)有着较宽的频段能量分布,较高的场强峰值以及较广的区域分布等特点,能够对数百至数千千米范围内的电子通讯装备造成损伤[1-2]。当电子器件或者系统工作在此环境中时,电磁脉冲会通过前门或后门耦合产生不同幅度的脉冲,进入电子器件内部造成干扰或损伤[3-4]。这其中,电源连接线缆往往是电磁脉冲耦合的重要途径[5]。并且,随着电子器件或系统的集成化程度更高、功耗更低、电源电平更低,这就带来了更小的噪声容限,再加上器件本身的同步开关噪声(SSN)[6],使得器件或系统的电源模块可能具有更高的电磁敏感性[7]。因此,研究这些器件和系统电源模块的电磁脉冲敏感性,实现更有效率的加固就显得十分必要。

器件或者系统的电磁脉冲敏感性实验研究,主要有辐照法[8-10]与注入法[11-14]。辐照法偏向于对实际应用环境的模拟复现,侧重于待测对象整体的电磁脉冲效应,不利于研究待测对象内部某个模块的电磁敏感性。而注入法是通过直接或间接方法,对待测对象内部某一模块注入幅值可变的电流脉冲,研究其电磁敏感性,更有利于找出敏感性高的模块,对后续更有针对性的加固有一定的指导意义。

如今,高速比较器与时钟驱动器广泛应用于各种电子系统或设备当中,而这些电子系统或设备的应用环境复杂多样,其中很有可能包含强电磁脉冲。而目前,针对这两种器件电源模块的电磁脉冲敏感性研究报道较少[15],因此,本文采用脉冲电流注入的实验方法,研究高速比较器与时钟驱动器电源模块的电磁敏感性。

-

选取型号为SB9696的高速比较器。将其配置为+5 V单电源供电,并且输入不同频率的正弦信号,探究其在不同工作频率下电源模块的电磁脉冲敏感性。正常工作状态下,其正端输出信号为不同频率的方波信号。

选取型号为SW946的时钟驱动器。工作电压为3.3 V,输入不同频率的信号,探究其在不同工作频率下电源模块的电磁脉冲敏感性。

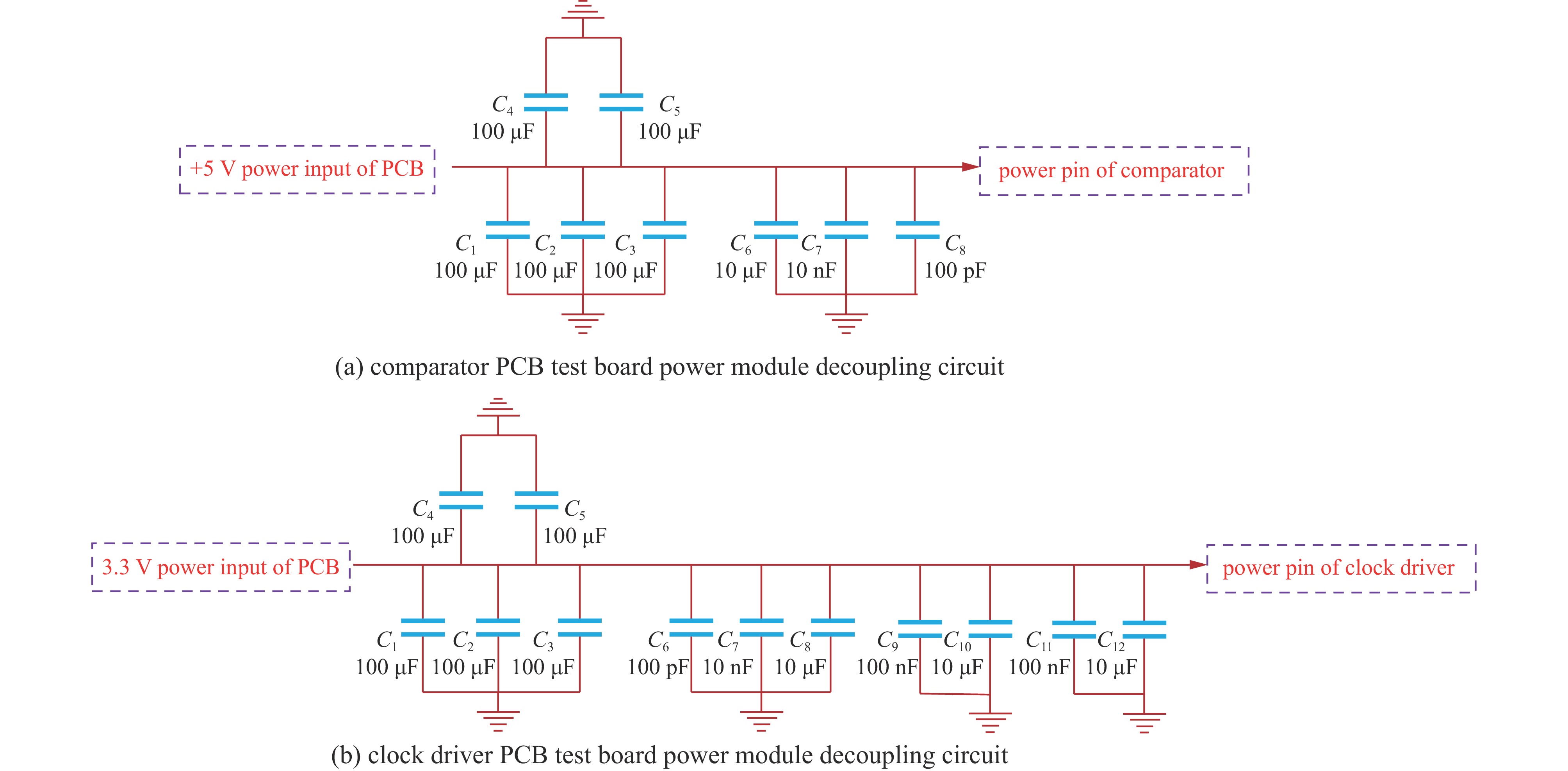

比较器与时钟驱动器芯片均设计了专门的PCB测试板进行脉冲电流注入实验,为了芯片能够在高频状态下稳定工作,在PCB测试板的电源分布网络(PDN)上添加了去耦电容,其电路原理图如图1所示。

-

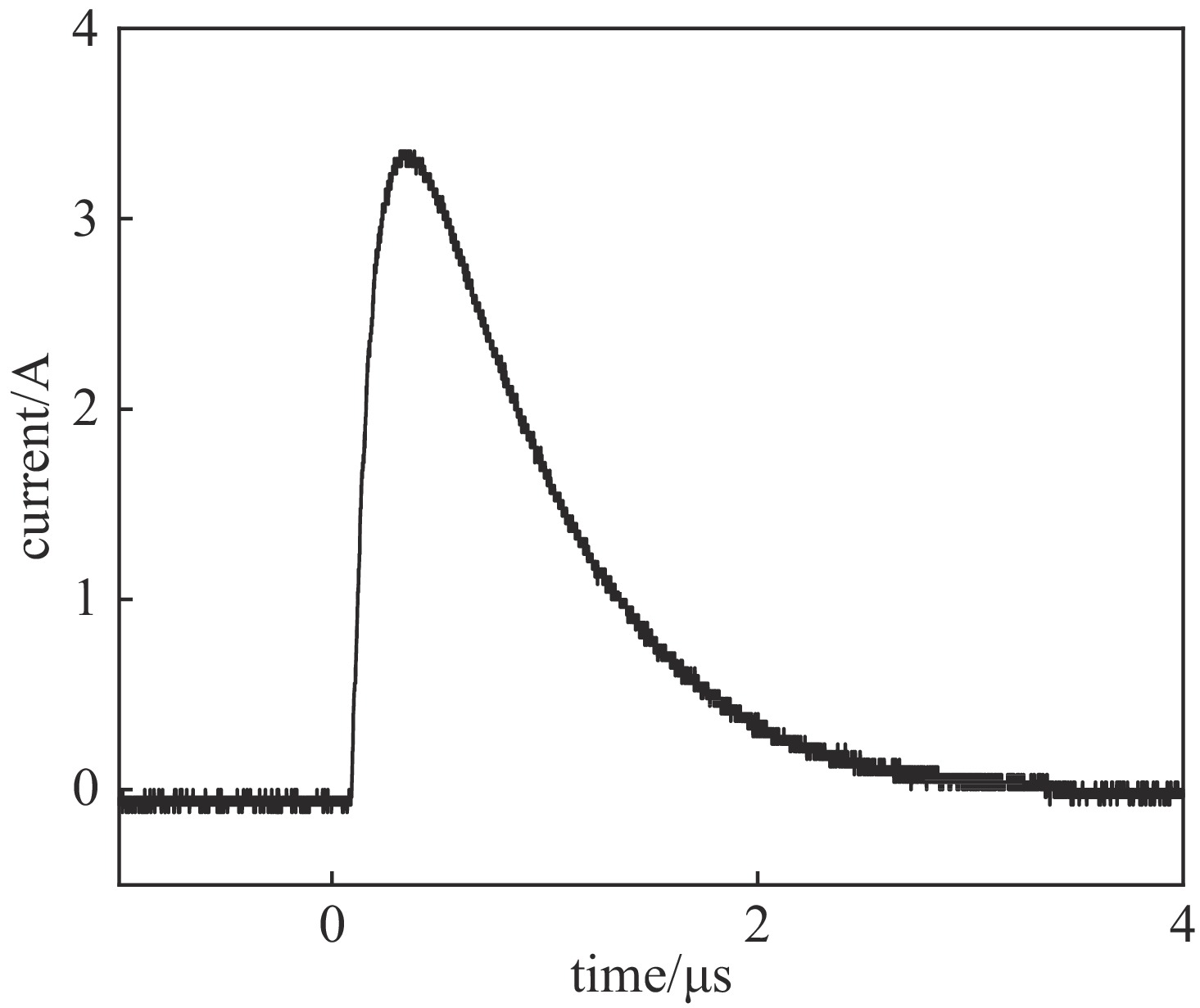

标准方波脉冲的波形参数及其在时域和频域的特征与HEMP传导环境波形差异较大。因此,在器件的敏感性效应表现与效应机理上可能存在差异。为了等效真实的HEMP环境[16],本文选择了注入HEMP传导波形,即20/500 ns双指数电流脉冲[17]。

-

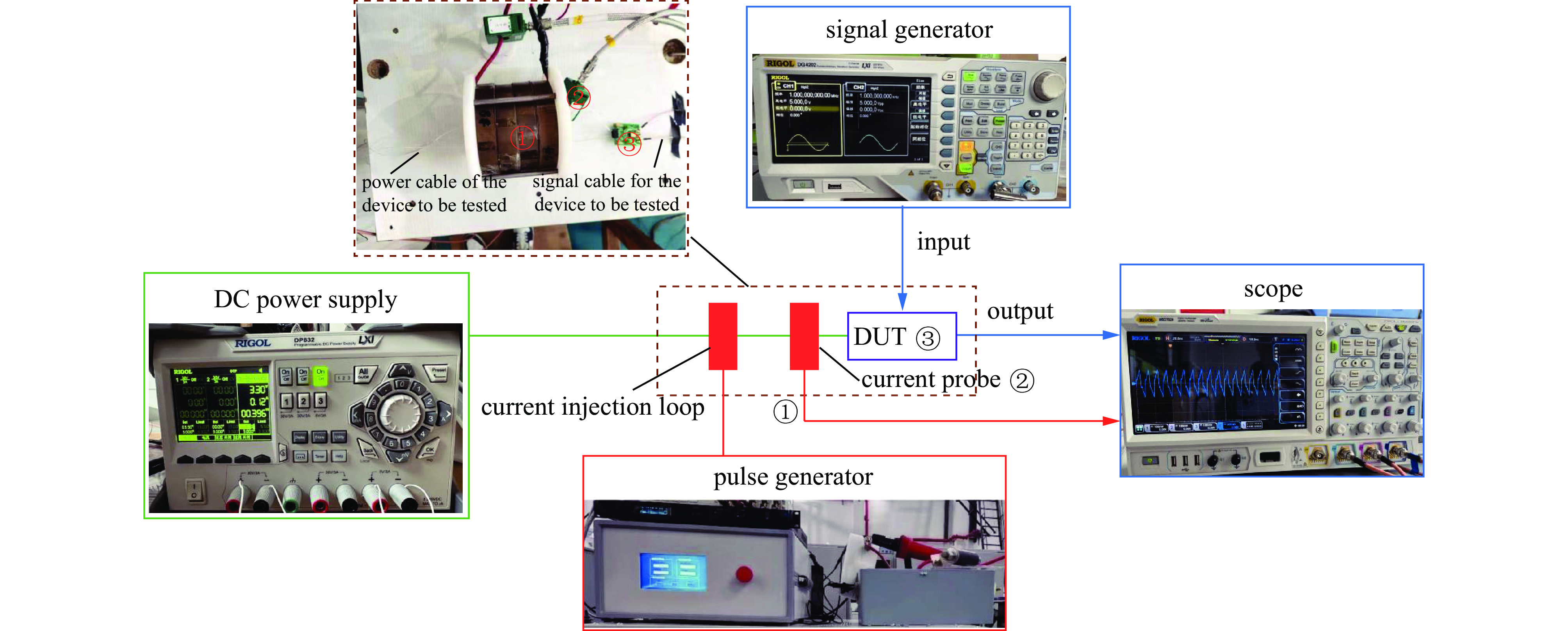

图2为脉冲电流注入实验配置实物示意图,采用两根长度约1 m的单线分别与电源和地连接。实验采用步进法,注入等级由低逐步提高,脉冲发生器步进为400 V,图3是电流探测环测得的注入电流波形。采用非接触式感性耦合的注入方法,对电源线缆进行脉冲电流注入。这种注入方法能够在待测器件正常工作的情况下进行电磁敏感性测试,更加符合实际情况[8]。同时,采用电流环接示波器的方法监测注入的脉冲电流大小。另外,比较器与时钟驱动器的输入信号由同轴线缆接信号发生器提供,输出信号也通过50 Ω同轴线连接示波器,监测其工作状态。

-

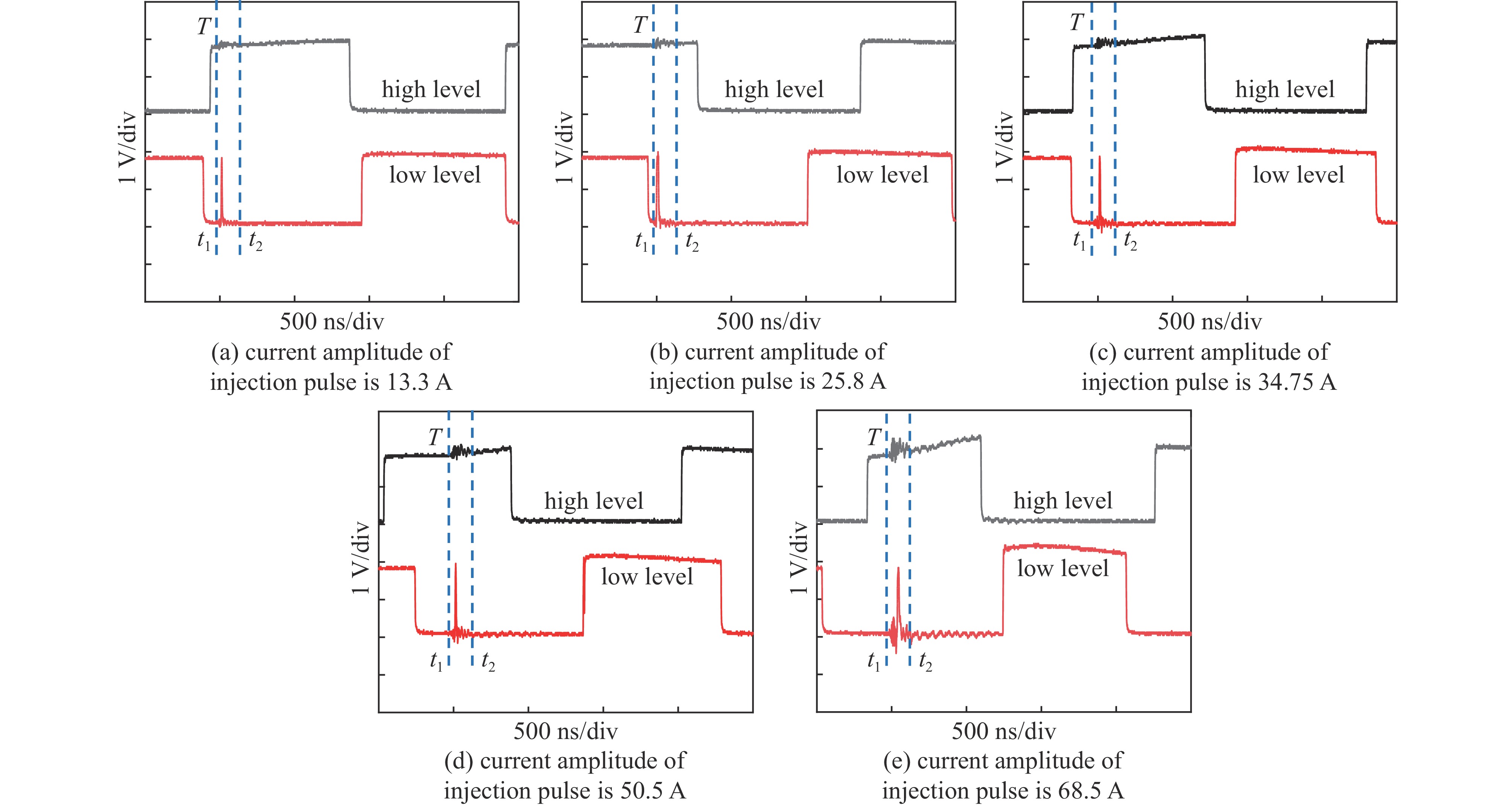

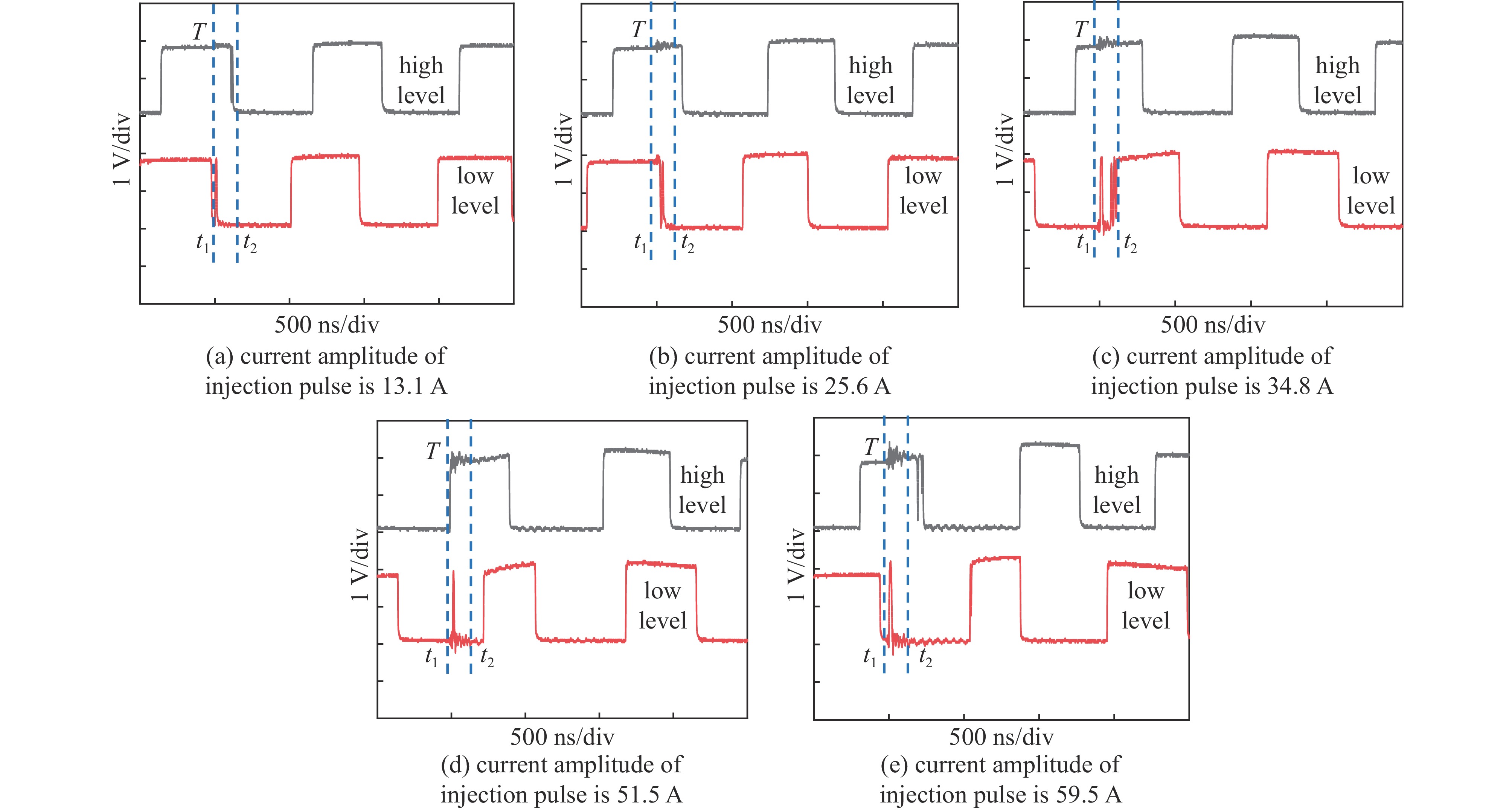

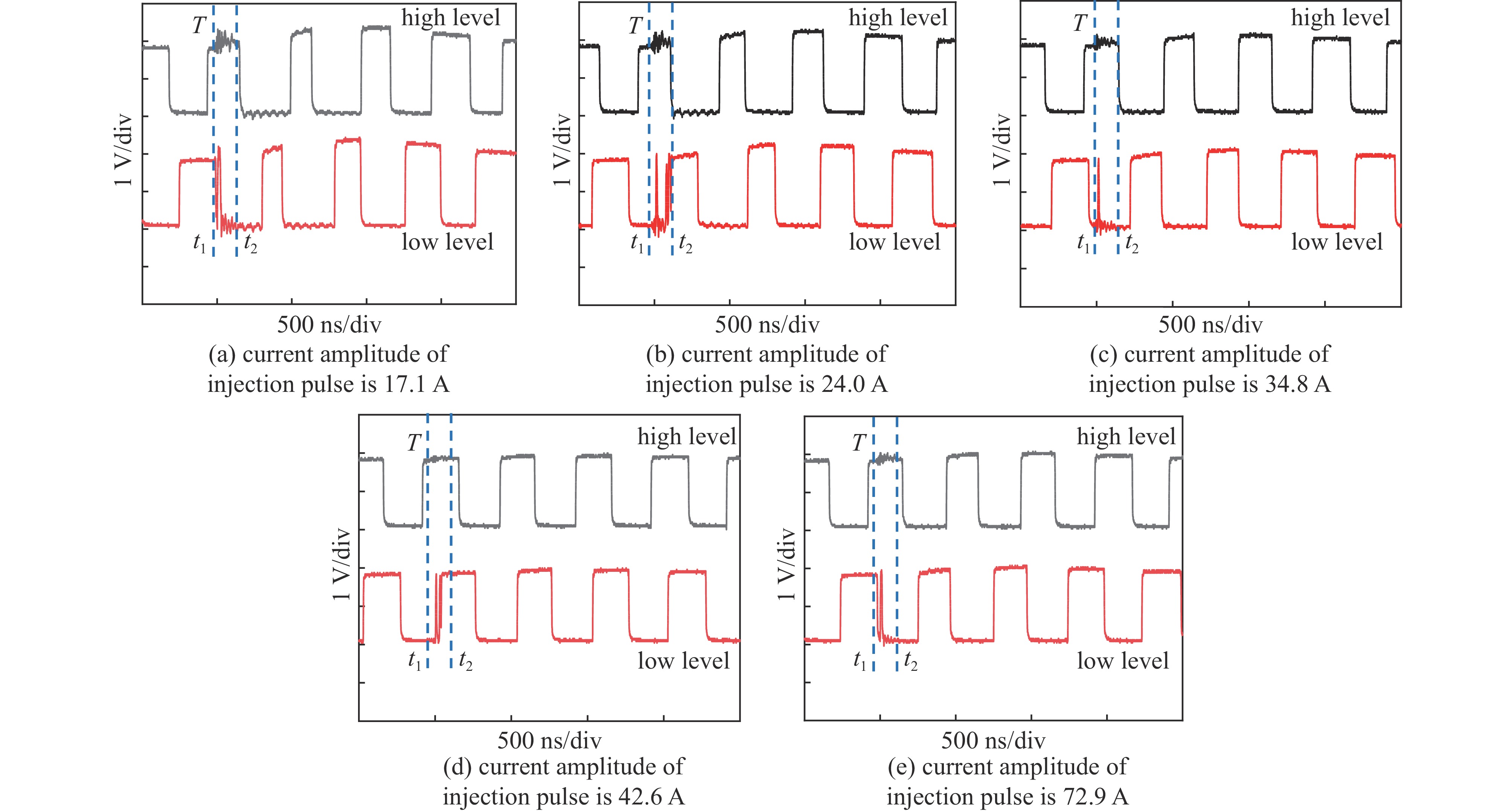

图4、图5和图6分别是比较器工作频率在500 kHz、1 MHz和2 MHz时,对电源模块注入不同幅值的电流脉冲,输出扰动出现在高电平与低电平时的波形。

由图4至图6可知,T时刻注入电流脉冲,t1−t2为比较器的输出扰动。在三种不同的工作频率下(500 kHz、1 MHz和2 MHz),当脉冲电流注入发生在比较器输出高电平时,随着注入脉冲幅值的增大,其输出产生振荡干扰,影响信息传递的质量,当脉冲电流注入发生在比较器输出低电平时,扰动会将比较器的输出电平拉高。在五种不同幅值的脉冲电流注入下,高电平处的振荡扰动都不足以改变比较器的输出信号逻辑(将“1”变为“0”),而低电平处的扰动能够改变其输出信号逻辑(将“0”变为“1”),造成信息的错误传递。如在注入较低幅值的电流脉冲时,高电平几乎没有扰动,而低电平的扰动已经能够改变输出信号逻辑。因此,比较器在不同的电平状态下电磁敏感性不同,低电平的敏感性明显高于高电平。这可能是因为比较器输出端口的防静电(ESD)保护电路[18-19],当扰动出现在低电平时ESD保护电路没有起作用,较小幅值的脉冲干扰就能够将低电平拉高,甚至改变输出逻辑,因此低电平表现出较高的电磁敏感性,而当扰动出现在高电平时,更高幅度的电压脉冲可能会对器件的输出端口造成损害,此时输出端口的ESD保护电路会将脉冲能量引出,降低电压扰动幅度,起到保护电路的作用。

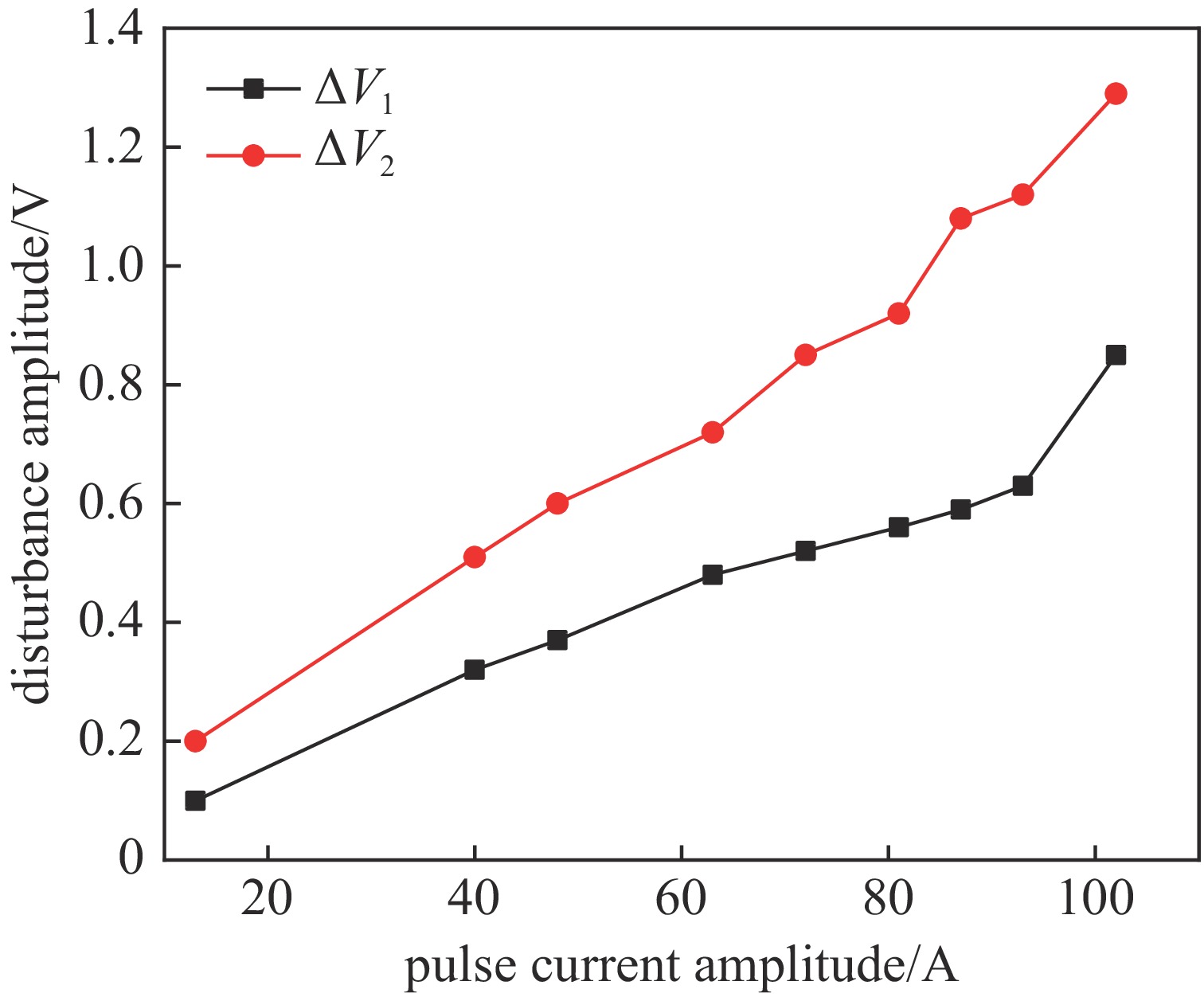

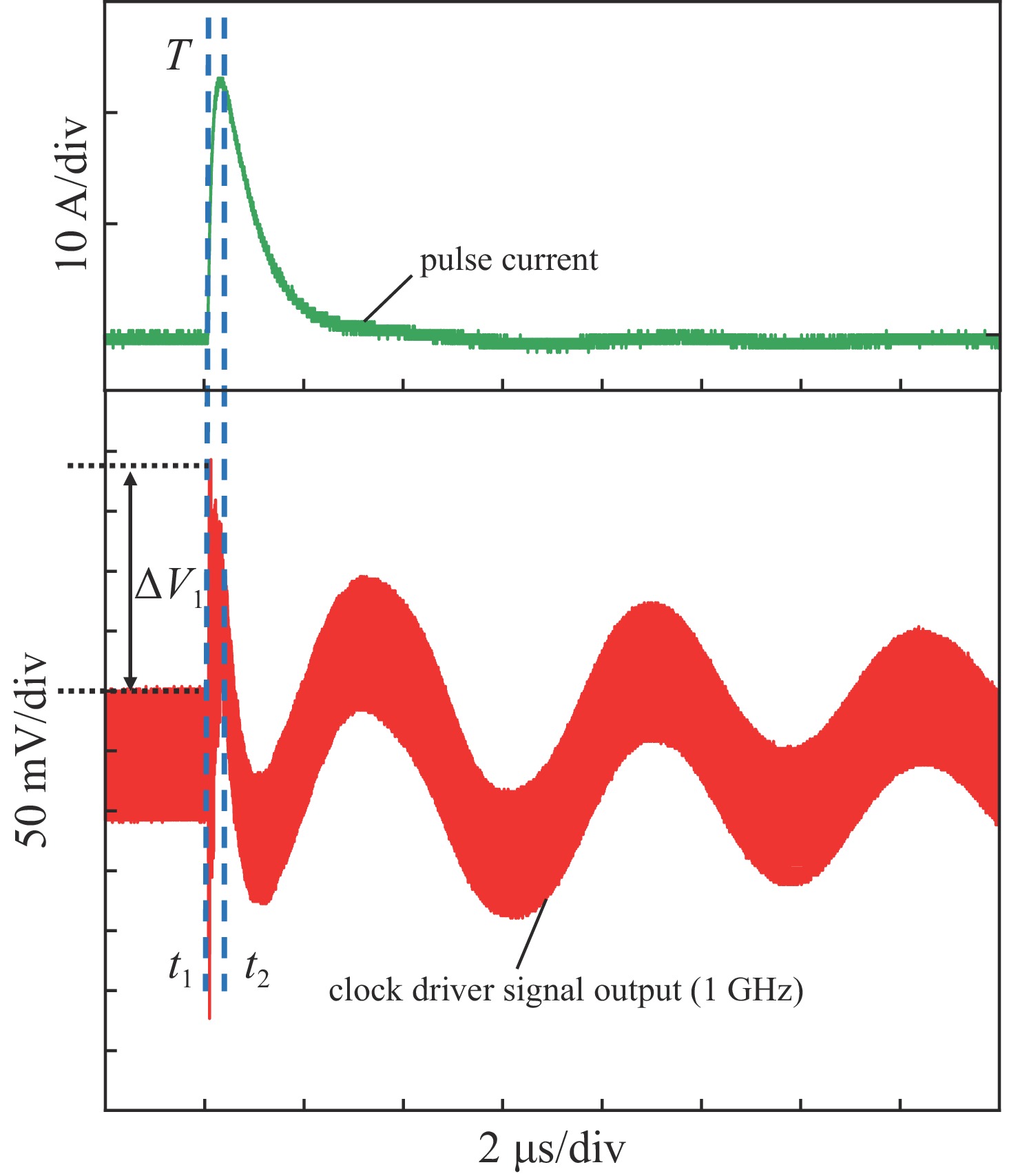

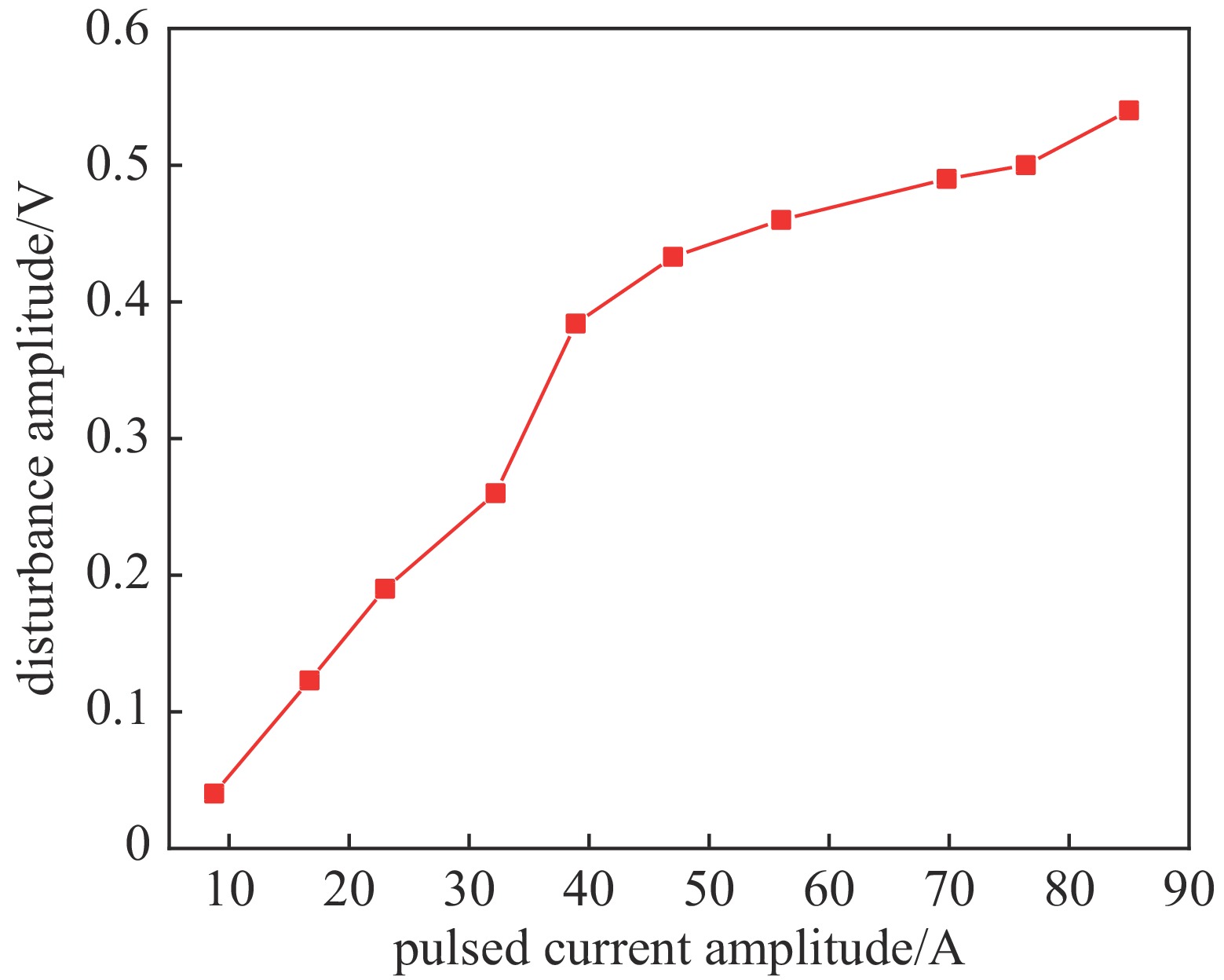

图7是比较器工作频率为10 MHz时,在T时刻注入脉冲电流,输出端口的扰动波形。图8是注入不同幅值的电流脉冲时,比较器输出信号的扰动幅度曲线。由图7可知,输出端口的扰动可分为两个阶段:第一阶段为注入脉冲电流时,输出端口的快速扰动,其扰动幅度为Δ

$ {V}_{1} $ ,此阶段扰动是比较器的电源模块注入双指数电流脉冲时,由于其具有较快的上升沿,而其PCB测试板的电源分布网络(PDN)存在一定的阻抗[20-22](以寄生电感为主),因此快速变化的电流能够在电源分布网络上产生$ \mathrm{\Delta } $ I噪声电压,且由图8可知随着注入电流逐渐增大,$ \mathrm{\Delta } $ I噪声电压越大,输出的扰动幅度Δ$ {V}_{1} $ 越大。第二阶段比较器输出波形表现出了一定程度的低频振荡,且由图8可知,注入电流脉冲幅值越大,低频振荡的幅度Δ$ {V}_{2} $ 越大。在对比较器进行脉冲注入实验时,脉冲发生装置也会对其所处的空间发射电磁波,并且空间中也可能存在其它电磁干扰而形成比较复杂的电磁场,此电磁场也可能会对比较器产生干扰,由此产生输出波形的第二阶段干扰,并且注入电流脉冲幅值越大,向空间发射的电磁波越强,对比较器的输出干扰就会越强,导致低频振荡的幅度Δ$ {V}_{2} $ 越大。图9是不同工作频率下,由注入电流脉冲引起的扰动Δ

$ {V}_{1} $ 随注入电流幅值的变化曲线。由图可知,不同的工作频率下,注入电流脉冲幅值越高,输出扰动越大。比较器工作频率越高,注入等幅值的电流脉冲,输出扰动越大。而在5 MHz与1 MHz下,等幅值的电流脉冲引起的输出扰动差距不大,10 MHz时输出扰动变化相对较大,这说明当比较器工作在较低频率下时,改变工作频率,电源的电磁敏感性对输出的扰动影响较小,而当工作频率逐渐增大时,电源的电磁敏感性对输出的稳定性影响变大。并且器件的工作频率越高,在干扰期间会引起更多的错误信息传递,不利于各模块之间的通讯。 -

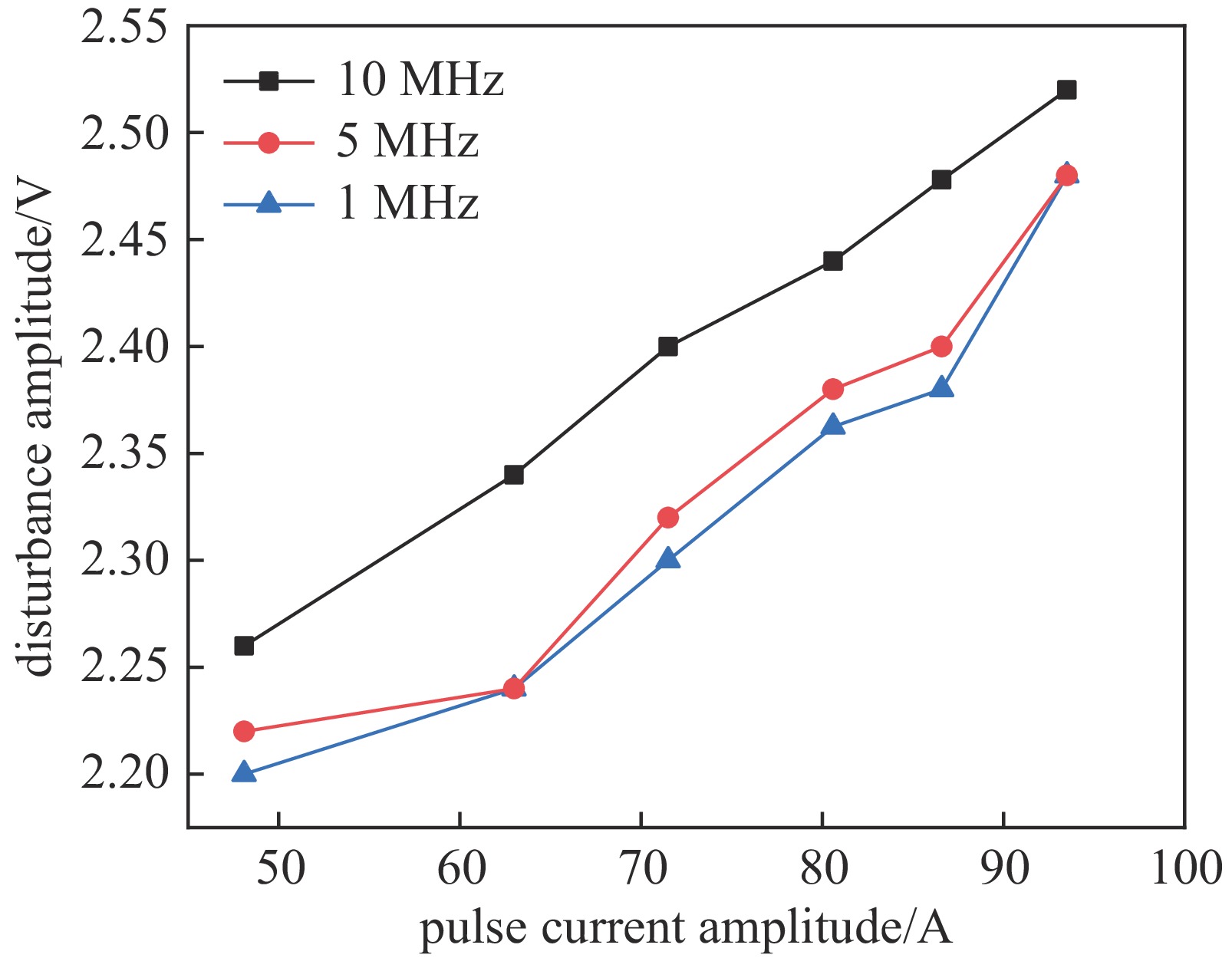

图10是工作频率为1 GHz,对时钟驱动器电源模块注入脉冲电流(幅值为23.2 A),其输出扰动波形。在T时刻注入脉冲,在脉冲上升沿期间(t1-t2)由于快速变化的电流引起了电源平面较大的噪声电压,使输出波形有明显的扰动。图11是注入不同幅值的脉冲电流,时钟驱动器输出信号的扰动幅度Δ

$ {V}_{1} $ ,由图可知,注入脉冲电流幅值越高,在PDN上产生的电压噪声越大,使输出扰动越大。大幅度扰动后,输出波形产生了低频振荡,且振荡的初始方向与扰动方向相反,这与比较器的输出振荡情况不同。因此,时钟驱动器的低频振荡可能是第一段大幅度扰动后器件对输出波形自我回调的过程,且振荡的幅度也逐渐变缓,最终趋于平稳。图12是1 GHz与500 MHz时钟驱动器输出波形扰动幅度Δ

$ {V}_{1} $ 随注入脉冲电流幅值变化的曲线。由图可知,在两个不同的工作频率下。时钟驱动器电源模块注入电流脉冲幅值越高输出的扰动越大。在等幅值的脉冲电流注入下,工作频率越高,输出扰动幅度越大。一方面,如图13所示,时钟驱动器输入功率不变,由于器件特性,频率越高输出信号的电平幅值越低,因此信噪比也会越低,导致输出信号的扰动幅度变大。另一方面,由于时钟驱动器工作在高频范围,电源平面的同步开关噪声(SSN)成为影响其输出稳定性的重要因素,因此工作频率越高,同步开关噪声会越大,导致电源模块稳定性变差,更容易受到电磁干扰,输出信号表现出较强的电磁敏感性。 -

本文采用脉冲电流注入法,对高速比较器与时钟驱动器的电源模块进行了实验研究,主要结论有:双指数电流脉冲快速变化的上升沿是影响高速比较器与时钟驱动器输出扰动的主要因素,并且注入幅值越高,会在电源分布网络引起更大的噪声电压,输出端口的扰动越大。高速比较器在不同的输出电平状态下电磁敏感性不同,低电平的敏感性明显高于高电平。这可能是由输出端口的ESD保护电路导致,当扰动出现在高电平,输出端口的ESD保护电路会将脉冲能量引出,降低电压扰动幅度,起到保护电路的作用。高速比较器工作频率较低时,改变工作频率,电源的电磁敏感性对输出的扰动影响较小,而当工作频率逐渐增大,电源的电磁敏感性对输出的稳定性影响变大。时钟驱动器电源模块的电磁敏感性易受到其工作频率的影响,工作频率越高、输出信号的信噪比越低且电源分布网络的同步开关噪声越大,导致电磁敏感性越高。

致 谢 感谢西北核技术研究院毛从光老师与秦锋老师给予的指导和帮助。

高速比较器与时钟驱动器电源模块电磁敏感性研究

Study on electromagnetic sensitivity of power modules of high-speed comparator and clock driver

-

摘要: 高空电磁脉冲(HEMP)能够对电子器件或系统产生不可忽视的电磁脉冲效应。选取高速比较器与时钟驱动器,采用脉冲电流注入(PCI)的实验方法研究这两种器件电源模块的电磁敏感性。试验结果表明:双指数脉冲电流的上升沿是引起高速比较器与时钟驱动器输出扰动的主要原因,且扰动幅度都受到注入脉冲电流幅值的影响;高速比较器工作在不同电平时电源模块的电磁敏感性不同;高速比较器与时钟驱动器在不同工作频率下会表现出不同的电磁敏感性。研究结果对电子器件或系统的电磁敏感性分析与加固具有一定的指导意义。Abstract: High altitude electromagnetic pulse (HEMP) can produce electromagnetic pulse effects on electronic devices or systems that cannot be ignored. In this paper, a high-speed comparator and a clock driver are selected, and the electromagnetic sensitivity of the power modules of these two devices is studied by the experimental method of pulse current injection (PCI). The test results show that the rising edge of the double exponential pulse current is the main cause of the output glitch of the high-speed comparator and clock driver, and the amplitude of the disturbance is affected by the amplitude of the injected pulse current. The electromagnetic sensitivity of the power module of the high-speed comparator is different at different output level. Different operating frequencies of high-speed comparators and clock drivers will show different electromagnetic sensitivity. The results have certain guiding significance for electromagnetic sensitivity analysis and hardening of electronic devices or systems.

-

-

-

[1] 毛从光, 程引会, 谢彦召. 高空电磁脉冲技术基础[M]. 北京: 科学出版社, 2019 Mao Congguang, Cheng Yinhui, Xie Yanzhao. Fundamentals of high-altitude electromagnetic pulse technology[M]. Beijing: Science Press, 2019 [2] 秦锋, 钟少武, 崔志同, 等. 核安保典型系统电磁脉冲效应试验研究[J]. 强激光与粒子束, 2019, 31:113201 doi: 10.11884/HPLPB201931.190219 Qin Feng, Zhong Shaowu, Cui Zhitong, et al. Experiment research on electromagnetic pulse effects of typical nuclear security system[J]. High Power Laser and Particle Beams, 2019, 31: 113201 doi: 10.11884/HPLPB201931.190219 [3] Camp M, Garbe H, Nitsch D. UWB and EMP susceptibility of modern electronics[C]//2001 IEEE EMC International Symposium. Symposium Record. International Symposium on Electromagnetic Compatibility. 2001: 1015-1020. [4] 崔志同, 毛从光, 孙蓓云, 等. LDO稳压器电磁脉冲损伤阈值试验研究[J]. 微电子学, 2013, 43(3):423-425 Cui Zhitong, Mao Congguang, Sun Beiyun, et al. Damage threshold characterization of LDO regulator for EMP interference[J]. Microelectronics, 2013, 43(3): 423-425 [5] 郑箘, 王璐静, 任凯琦. 强电磁脉冲对计算机电缆的注入毁伤效应研究[J]. 无线电工程, 2016, 46(8):79-82 Zheng Jun, Wang Lujing, Ren Kaiqi. Study on damage effect of high electromagnetic pulse injecting computer cable interfaces[J]. Radio Engineering, 2016, 46(8): 79-82 [6] 李君. 系统级封装的电源完整性分析和电磁干扰研究[D]. 成都: 西南交通大学, 2010: 10-27 Li Jun. The power integrity analysis and electromagnetic interference study in system-in-package[D]. Chengdu: Southwest Jiaotong University, 2010: 10-27 [7] Mejecaze G, Dubois T, Curos L, et al. Failure scenario of power supply due to conducted electric pulse from E1 HEMP[J]. IEEE Transactions on Electromagnetic Compatibility, 2023, 65(2): 464-474. doi: 10.1109/TEMC.2022.3227335 [8] 王书平, 刘尚合, 侯民胜. 核电磁脉冲对单片机系统的辐照效应研究[J]. 军械工程学院学报, 2002, 14(1):11-15 Wang Shuping, Liu Shanghe, Hou Minsheng. Study on irradiation effects of nuclear electromagnetic pulse to single chip computer system[J]. Journal of Ordnance Engineering College, 2002, 14(1): 11-15 [9] 韩军, 谢彦召, 翟爱斌, 等. 静态随机存储器的电磁脉冲效应实验研究[J]. 核电子学与探测技术, 2010, 30(11):1423-1426 Han Jun, Xie Yanzhao, Zhai Aibin, et al. Experimental investigation on EMP effect of SRAM[J]. Nuclear Electronics & Detection Technology, 2010, 30(11): 1423-1426 [10] 郭艳辉, 李子森, 杨宝山, 等. 国外计算机强电磁脉冲敏感度实验结果的研究[J]. 安全与电磁兼容, 2014(3):67-70 Guo Yanhui, Li Zisen, Yang Baoshan, et al. Study of results on computer system HPEM susceptibility researched abroad[J]. Safety & EMC, 2014(3): 67-70 [11] 史建永. 高空核电磁脉冲电流注入方法研究[D]. 石家庄: 石家庄铁道大学, 2021: 1-7 Shi Jianyong. Research on high-altitude nuclear electromagnetic pulse current injection method[D]. Shijiazhuang: Shijiazhuang Tiedao University, 2021: 1-7 [12] 崔志同. HEMP脉冲电流注入的仿真与实验研究[D]. 西安: 西安电子科技大学, 2020: 1-10 Cui Zhitong. Simulation and experimental research on HEMP pulsed current injection[D]. Xian: Xidian University, 2020: 1-10 [13] 陈明, 程引会, 吴伟, 等. 80C196KC单片机电磁脉冲效应模拟实验研究[C]//第八届全国抗辐射电子学与电磁脉冲学术交流会论文集. 2005: 442-445 Chen Ming, Cheng Yinhui, Wu Wei, et al. Simulation experiment of electromagnetic pulse effect by 80C196KC microcontroller[C]//The 8th National Anti-radiation Electronics and Electromagnetic Pulse Academic Exchange Conference. 2005: 442-445 [14] Kwak S, Nah W, Kim S. Electromagnetic susceptibility analysis of I/O buffers using the bulk current injection method[J]. JSTS: Journal of Semiconductor Technology and Science, 2013, 13(2): 114-126. doi: 10.5573/JSTS.2013.13.2.114 [15] Li Chengjin, Liu Yuan, Liu Jianbo, et al. Electromagnetic interference effects in the bipolar voltage comparators[C]//2014 10th International Conference on Reliability, Maintainability and Safety (ICRMS). 2014: 185-188. [16] 夏德威, 杜传报, 曹菲, 等. 低噪声放大器电磁脉冲效应表征和阈值分布函数确定方法[J]. 现代应用物理, 2021, 12:040504 Xia Dewei, Du Chuanbao, Cao Fei, et al. Effects characterization of low noise amplifier and determination of threshold distribution function to high-altitude electromagnetic pulse[J]. Modern Applied Physics, 2021, 12: 040504 [17] Du Chuanbao, Xia Dewei, Huang Quan, et al. Research on electromagnetic susceptibility of electronic modules in component-level HEMP PCI test[J]. Energies, 2022, 15: 1409. doi: 10.3390/en15041409 [18] Guo Yaxin, Li Yang, Li Junlin, et al. Experimental study of transient dose rate effects of two level-shifting transceivers and simulations on their ESD circuits[J]. IEEE Transactions on Nuclear Science, 2022, 69(5): 1157-1166. doi: 10.1109/TNS.2022.3140555 [19] Huang Kaiping, Peng Polin, Chu Liwei, et al. ESD protection diode with guard ring layout optimized for latch-up immunity enhancement in FinFET technology[C]//2019 41st Annual EOS/ESD Symposium (EOS/ESD). 2019: 1-4. [20] 张翰宗. 系统级封装中电源完整性的分析与研究[D]. 西安: 西安电子科技大学, 2017: 5-12 Zhang Hanzong. Analysis and investigation of power integrity for system-in-package[D]. Xian: Xidian University, 2017: 5-12 [21] 房丽丽, 章传芳. ANSYS信号完整性和电源完整性分析与仿真实例[M]. 北京: 中国水利水电出版社, 2018 Fang Lili, Zhang Chuanfang. ANSYS signal integrity and power integrity analysis and simulation examples[M]. Beijing: China Water&Power Press, 2018 [22] 周润景, 王洪艳. 基于Cadence的信号和电源完整性设计与分析[M]. 北京: 电子工业出版社, 2017 Zhou Runjing, Wang Hongyan. Signal and power integrity design and analysis based on cadence[M]. Beijing: Publishing House of Electronics Industry, 2017 -

首页

首页 登录

登录 注册

注册

下载:

下载: