-

近年来,随着5G、物联网、自动驾驶等新型产业的兴起,作为信息技术产业核心基础的集成电路产业也得到快速发展[1]。基于此类新兴信息产业在工作生活中的广泛应用,人类社会会产生海量的数字信息资源,对这些信息的存储与分析需求亦促进了存储芯片产业的快速发展,即单位体积拥有更多存储容量的高性能芯片。为此,存储芯片的高性能不仅要从结构上从二维(2D NAND)向三维(3D NAND)转换[2],在生产制造工艺和产线工程端也有着更高的需求。

化学机械研磨(Chemical Mechanical Planarization,CMP)工艺是芯片制造过程中的核心工艺之一,其能够实现晶圆表面的整体平坦化,保证晶圆表面薄膜的厚度均匀性[3]。3D NAND存储芯片有着高堆叠层数和高深宽比深孔结构的特点,其对CMP工艺厚薄膜移除及表面均匀性提出了更高的要求。同时,随着3D NAND技术节点的发展,即堆叠层数的增加,其对CMP工程化要点,如设备配置、工艺布局等也有着重要的影响。本文以3D NAND典型芯片结构为基础,对不同CMP制程的工艺原理和特点、不同节点下的CMP设备配置关系进行了分析研究,以期能够促进CMP工艺工程在3D NAND中的发展。

全文HTML

-

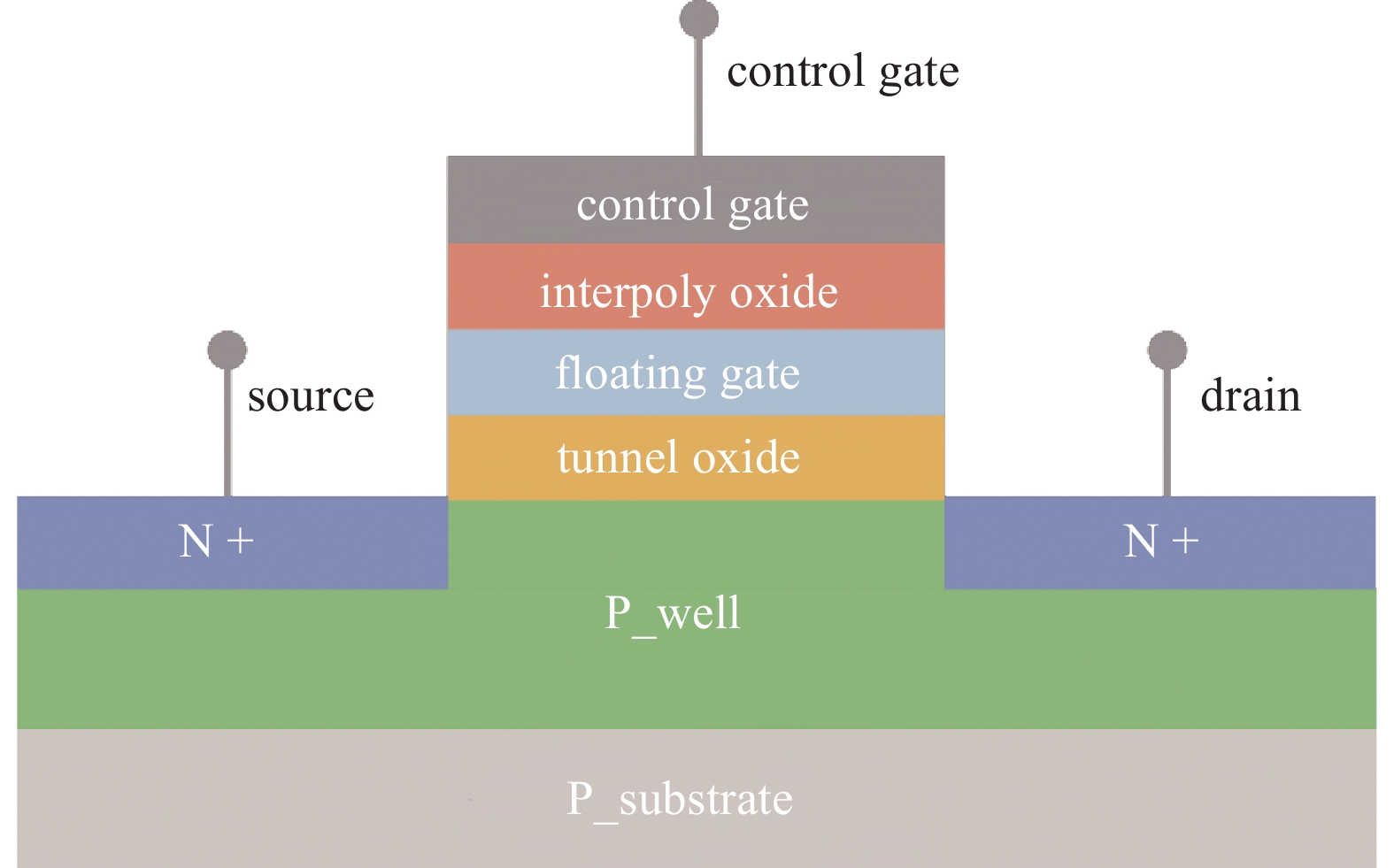

存储芯片是一种以电信号存储方式工作的存储器,以DRAM、Nor Flash和NAND Flash为主。其中,NAND Flash因为存储及擦除信息速度快、存储密度高、成本低等优点,近年来发展迅猛[4,5]。如图1所示,为一个NAND Flash基础存储单元,为浮栅型结构。当存储单元执行写入操作时,P阱中电子会注入浮栅中,此时其处于逻辑“1”状态;当进行擦除操作时,浮栅中电子被“放逐”至P阱中,此时处于逻辑“0”状态,NAND Flash通过改变控制栅极的阈值电压进行存储控能。

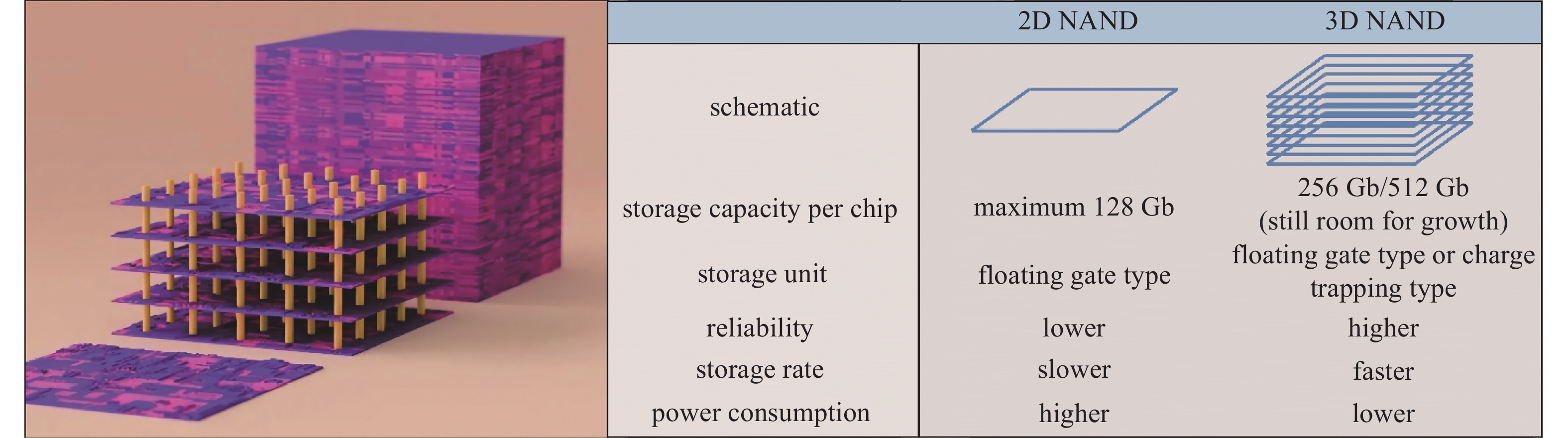

随着技术与需求的发展,平面2D NAND Flash的栅极结构和氧化层逐渐减小与变薄,从而导致了器件可靠性能的降低,逐渐不能满足大容量、高速率的产品需求。因此,NAND Flash的发展开始转向三维空间,即3D NAND,常见的方法为将二维平面结构进行垂直构造,通过一个圆柱形的沟道来制备电荷俘获单元,从而在保证性能的同时能够实现更大的存储容量,如图2所示为2D与3D NAND Flash的性能对比。

对于3D NAND芯片结构来说,其通常由CMOS驱动电路和Array存储阵列两部分组成,当前主流技术架构可分为CMOS Under Array(CUA)[6]和X-tacking[7]两种。其中按Array部分的工艺路线可分为四种技术路线:TCAT(Terabit Cell Array Transistor)、BiCS(Bit Cost Scalable)、P-BiCS(Pipe-Shaped Bit Cost Scalable)和FG(Floating Gate),如表1中为四种技术路线的优劣对比。在3D NAND制造中,CUA的芯片架构通常是先进行CMOS驱动电路结构的制备,在其基础上再进行Array存储结构的制备,这种架构的缺点有在后续的阵列加工部分会涉及高温高压的工艺,会对之前的逻辑电路产生影响;同时,CMOS外围电路占整个芯片的面积无法减少,芯片上总有部分面积无法实现存储作用,使得芯片利用率低;此外,先外围电路再阵列制造时,如发现问题再进行工艺调整使得整个研发制造周期变长。而对于X-tacking来说,其通过将CMOS和Array分开加工,外围电路不受影响,提高了存储的面积利用率,也缩短了研发生产周期。随着存储需求的不断增加,Array阵列的堆叠层数也将成倍增高,X-tacking将成为未来3D NAND闪存主流技术架构的发展趋势。

因此,本文以X-tacking技术为基础,进行CMP工艺及其设备配置的分析研究工作。

-

在3D NAND X-tacking制备中,CMOS结构和Array结构分别为两片晶圆进行制造,但对于CMP制程来说,其可以分为氧化物研磨(Oxide CMP)、多晶硅研磨(Poly-Si CMP)和金属研磨(Metal CMP)三类,其分别在不同的制造阶段对相应的功能层进行平坦化作用。

-

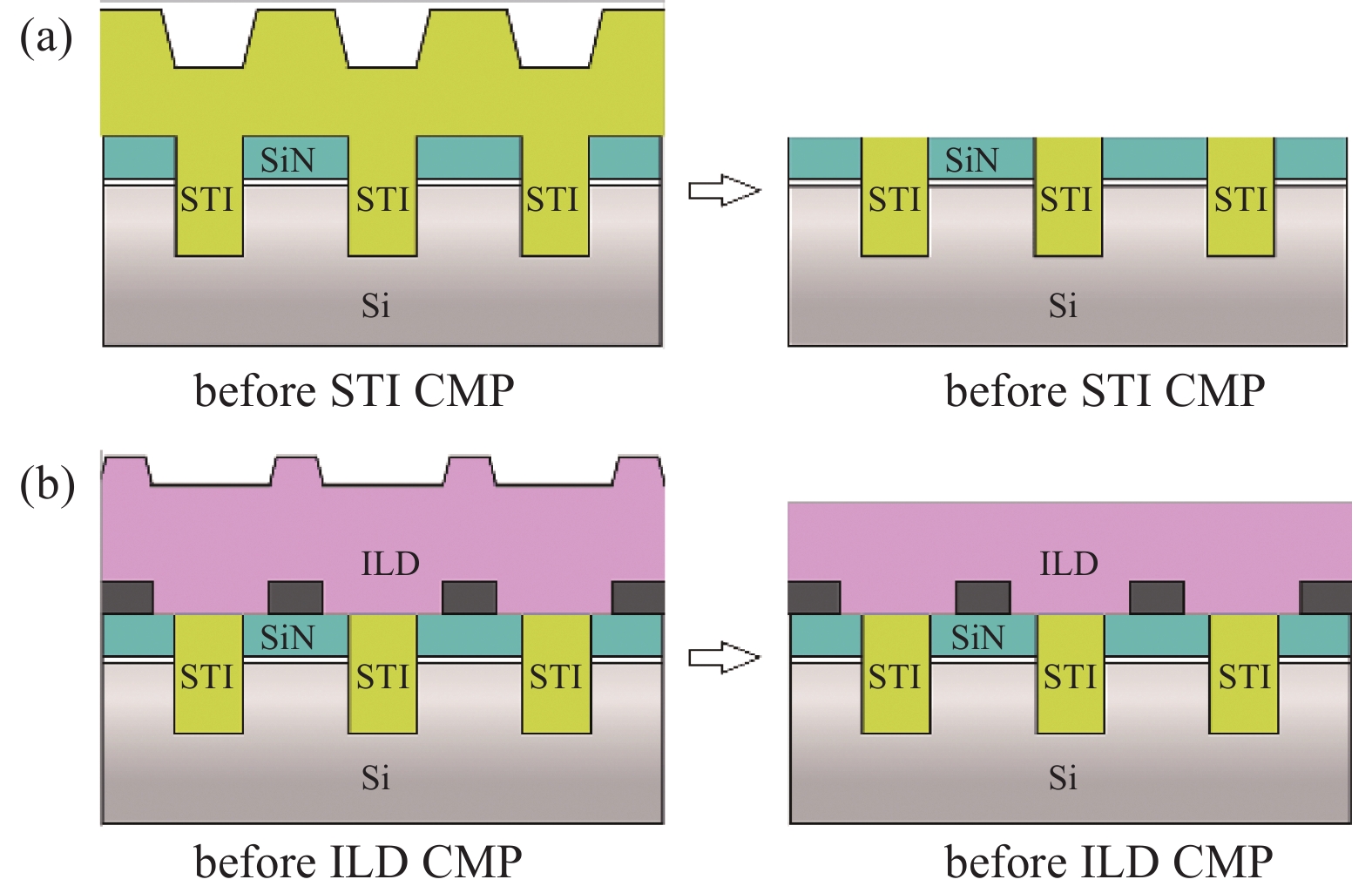

在3D NAND制备中,Oxide CMP包含浅沟槽隔离(Shallow Trench Isolation CMP,STI CMP)和层间电介质(Inter-Layer Dielectric CMP,ILD CMP)两种类型。STI CMP工艺制程一般在用于制备CMOS阶段,STI是用氧化层将两个门电路之间隔离开,使得门电路之间互不导通[8]。这种技术是先在门电路预留位置的两侧进行沟槽结构的刻蚀,接着在沟槽中进行氧化层的沉积,由于沟槽结构与两侧存在高度差,沉积薄膜呈现高低起伏结构。STI CMP主要就是将沟槽结构以外的薄膜层进行研磨移除,停在氮化硅(SiN)上,见图3(a),由于在研磨过程中要接触到不同的薄膜层,其能否准确的停止在SiN表面是STI CMP制程的关键因素,如果提前停止研磨会造成表面薄膜研磨不够,而过量研磨会使得STI内的薄膜厚度减少,影响芯片良率。

ILD CMP也可称Oxide CMP,是由于其研磨过程主要移除的薄膜为氧化物。ILD是用氧化层将不同功能层之间进行隔离,使得层与层之间、金属导线之间不导通[9]。一方面,ILD介质层较厚,因此研磨过程对研磨速率的需求较高,可以通过选用不同类型的研磨液进行提升;另一方面,ILD CMP整个过程主要是对氧化硅的研磨,是一种薄膜内停止的研磨过程,其在研磨过程中移除一定厚度薄膜且不接触到两种薄膜的界面,如图3(b)。因此,对其停止点的精准监测是其核心需求之一。

-

3D NAND Array单元中,在形成具有高深宽比的竖向沟道中,需要沉积Poly进行连接作用。Poly CMP工艺中是将多晶硅薄膜进行研磨,停止在其它氧化物界面层,其过程原理与STI CMP类似,利用研磨浆料对不同介质材料的高选择比,在停止层界面感应研磨转盘扭矩的变化进行研磨过程的停止,在此不再赘述。

-

在3D NAND制备中,Metal CMP包含金属钨 (W CMP)和金属铜 (Cu CMP)两种类型[10]。

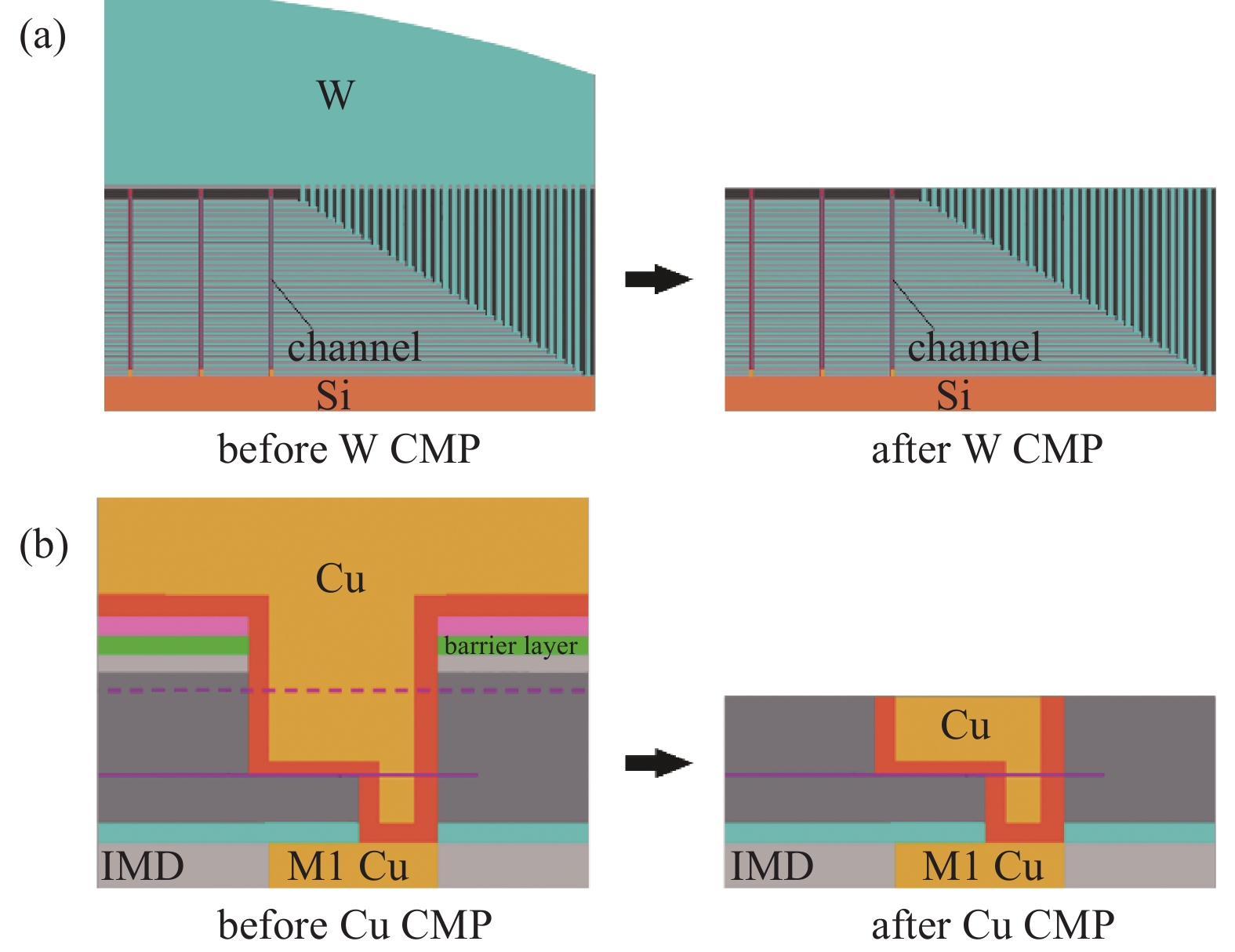

W CMP主要应用于CMOS的金属连接和Array中的位线金属连接[11]。对于W CMP工艺来说,其是一种金属化学机械研磨过程,金属与研磨浆料接触时,浆料中的氧化剂会将金属表面进行氧化形成金属氧化物,保护内部的金属进一步氧化,同时,在研磨垫和研磨粒子的机械作用下,将氧化的金属氧化层进行移除,将金属表面再次暴露重复氧化过程和氧化物移除过程。与STI CMP类似,W CMP也是一种薄膜间停止的CMP工艺,如图4(a),研磨过程为先将表面的钨金属进行快速研磨,当其研磨至表面出现氧化物层时进行停止,再通过精细研磨过程将表面氧化物进行移除,将钨栓塞稍露出一部分,以便于进行后续的金属互连过程。

Cu CMP是用于后段铜金属互连工艺薄膜的平坦化,其主要是应用大马士革工艺,如图4(b),即先在氧化物层上刻蚀出互连孔洞或者沟槽,再进行铜金属的沉积,沉积之后再利用Cu CMP工艺将铜金属层移除,从而得到铜互连层[12]。在3D NAND的制备中,Cu CMP通常用在CMOS和Array制备部分的后段金属互连。与W CMP相同,Cu CMP也是金属平坦化,其停止点在金属与氧化层的界面,属于薄膜层间停止。对于铜金属来说,其易于向侧壁与基底进行扩散,因此在沉积铜金属层之前要先沉积一层隔绝层(barrier layer),在Cu CMP过程中要充分考虑隔绝层的因素进行设备与耗材的选择。此外,后段铜金属层相较于前段氧化层更厚,在研磨过程中晶圆与研磨垫之间的摩擦温度会影响到研磨效果,更厚的铜金属层所需研磨速率应更高,以减少研磨时间从而弱化摩擦高温对晶圆表面的影响。

2.1. Oxide CMP

2.2. Poly CMP

2.3. Metal CMP

-

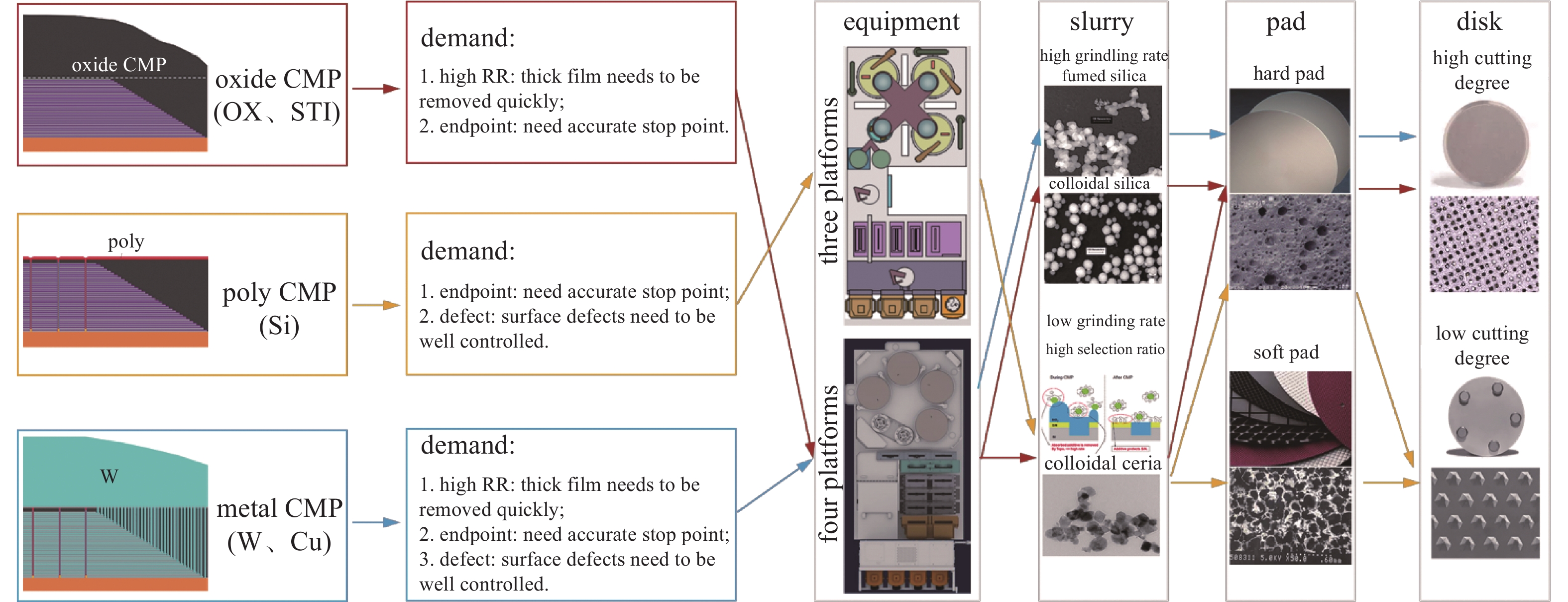

对于半导体项目,工艺设备是其整个生产线的核心,设备类型的选择能够直接影响产品良率、生产效率、投资成本等多方面。半导体工艺设备类型的选择,应首先分析对应工艺制程的需求特点,不同的制程对设备的需求不同,针对特定工艺需求分析不同设备的功能特点,将两者进行有机匹配,综合考虑成本单价因素,从而确定设备的类型。如图5所示,对于CMP工艺设备的选型,其主要在研磨速率、停止点和表面缺陷上有着特定需求,并且对于设备的耗材,例如slurry、pad和disk等同样有着不同的要求和选择[10,13,14]。

3D NAND芯片制备有着沉积薄膜厚和表面凹凸结构复杂的特点,因此对CMP工艺设备类型的选择应以上述特点为基础进行。以STI CMP为例,其薄膜移除过程通常要经过三个阶段,分别称为P1、P2和P3。P1是快速平坦化阶段,使用的研磨浆料和研磨垫均是能够快速移除氧化物薄膜的类型;P2是薄膜停止点阶段,使用具有高选择比的研磨浆料(如二氧化铈颗粒),同时需要在研磨转盘中配置高灵敏度的扭矩感应器,通过监测研磨垫与晶圆之间薄膜介质的摩擦力变化,进行系统端研磨过程的停止;P3是对晶圆精细研磨修整阶段,通常是使用软质的研磨垫结合高纯水或特殊化学试剂,对晶圆表面进行精细研磨,去除P1、P2阶段的研磨杂质和表面微小缺陷,薄膜移除量极低。因此STI CMP制程可选择AMAT公司的Reflexion LK设备,其具有三个旋转研磨盘,且在P2的研磨盘上配备有高灵敏度的扭矩感应器,同时搭配合适的研磨耗材,能够满足STI CMP的工艺需求。

Poly CMP的设备选择与STI CMP选择类似,在此不再赘述。

Oxide CMP所用设备通常也具有三个研磨转盘,其P1、P2、P3的耗材配置通常是相同的,对于Oxide CMP来说,其对于设备的需求主要是在于对厚度的掌控。由于没有不同材质薄膜层充当停止层,其设备必须依靠一套制程自动控制系统(Auto Program Control,APC)进行薄膜厚度的控制,并通常会配置有小型的量测设备,从而保证晶圆量测率在100%,也能够及时将量测结果进行系统反馈。

对于W CMP的工艺过程,同样使用具有三个研磨转盘的设备,在P1阶段,主要是利用高研磨速率的浆料和研磨垫将钨金属快速移除;在P2阶段,不仅要将金属钨薄膜层移除,还要将金属钨下的Ti/TiN薄膜层移除,露出能够进行光反射的氧化物层。在此阶段,需要在研磨转盘中配置激光器与感应器,同时需使用具有透光窗口的研磨垫,当研磨至氧化物层时可将光线进行反射,通过感应器的感应使得研磨过程停止,从而能够使得薄膜层准确停在界面层上;在P3阶段,应使用对氧化物与钨具有高选择比的浆料,即对氧化物研磨速率快,对金属物研磨速率慢,从而在精细研磨过程中能够将钨栓塞露出氧化物层表面,有利于后续金属互连的工艺。

对于Cu CMP工艺来说,其应用设备的研磨转盘个数可选三个或四个,以三个转盘的设备为例,在P1阶段,与其它CMP工艺类似,是将金属薄膜进行快速移除的过程,但不同的是,由于沉积的金属铜厚度较厚,能够达到微米级别,在研磨过程中其表面平整度会有较大的变化,这就需要对设备的P1转盘引入实时过程控制系统(Real Time Process Control,RTPC)[15]。此系统能够实时动态的调节研磨头中各个区域的下压力,使得铜薄膜表面保持较均一的平整度;在P2阶段,与W CMP类似,要通过对氧化物层反射光线的探测进行研磨过程的停止,一般称为全域扫描(Full Scan)技术;P3阶段主要是对氧化物层表面铜阻挡层的研磨过程,从而需要对研磨浆料有着高选择比的需求,即在对阻挡层进行研磨的同时,对铜金属的研磨速率慢,从而达到有效移除阻挡层的作用。对于3D NAND制备中不同CMP制程的设备选型,如表2所示。

-

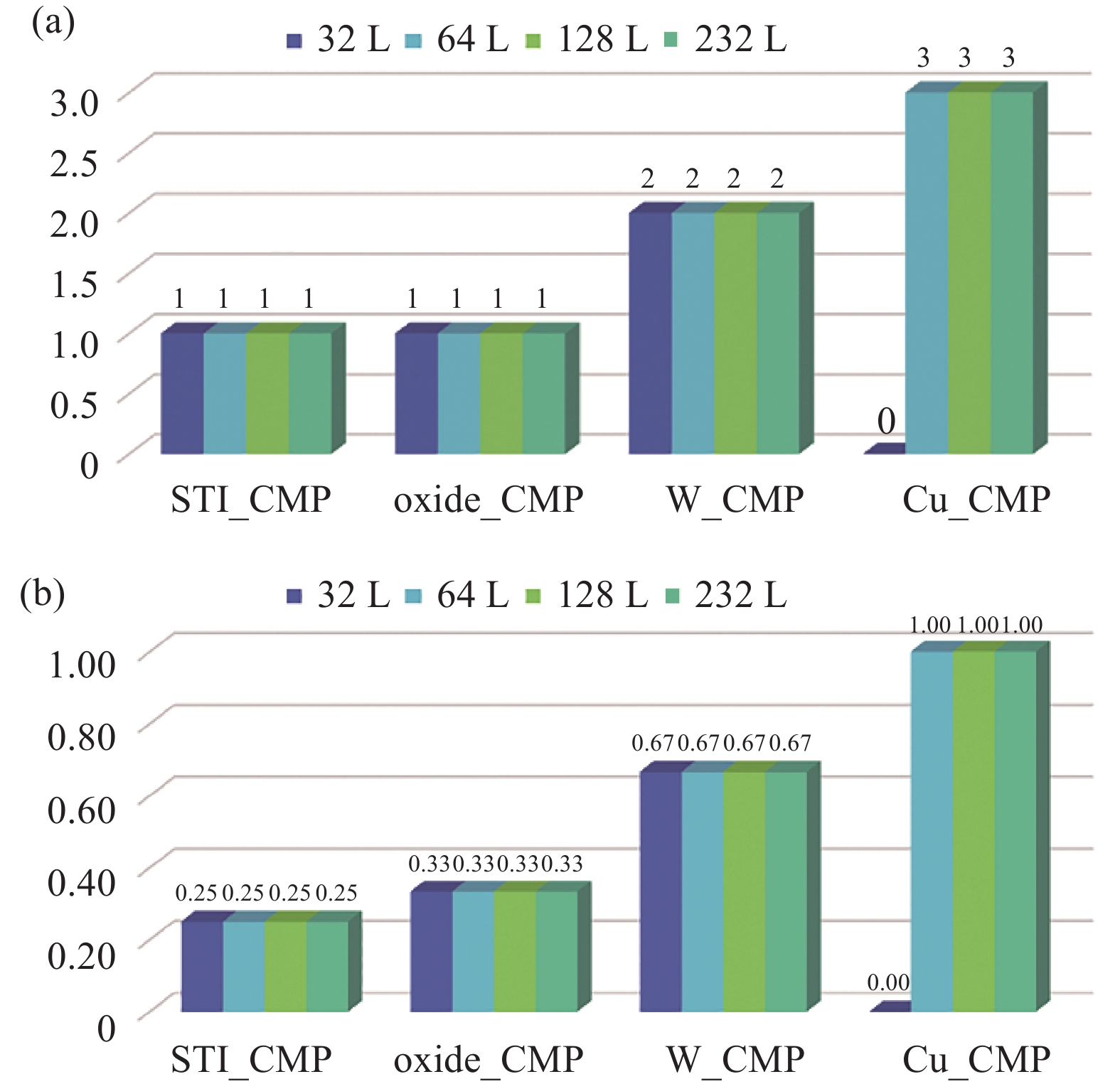

对于X-tacking技术来说,其CMOS部分和Array部分分别是两片晶圆进行制备,在制备CMOS控制电路时所包括的CMP制程有STI CMP、Oxide CMP、W CMP和Cu CMP。CMOS部分的CMP工艺次数和设备数量配置如图6(a)和6(b)中所示,1次STI CMP工艺形成浅沟槽隔离结构,1次Oxide CMP工艺形成中间介质层,2次W CMP形成钨栓塞和第一金属互连层,3次Cu CMP形成铜金属互连层,32L时CMOS部分未用到Cu CMP制程。另一方面,由于薄膜厚度的增加只发生在Array部分,CMOS部分各薄膜厚度未发生变化,因此其对应的设备数量(已做归一化处理)也应未发生变化。本文中的CMP设备数量,是基于不同技术节点下,对已有项目的相关数据进行理论推导得出。

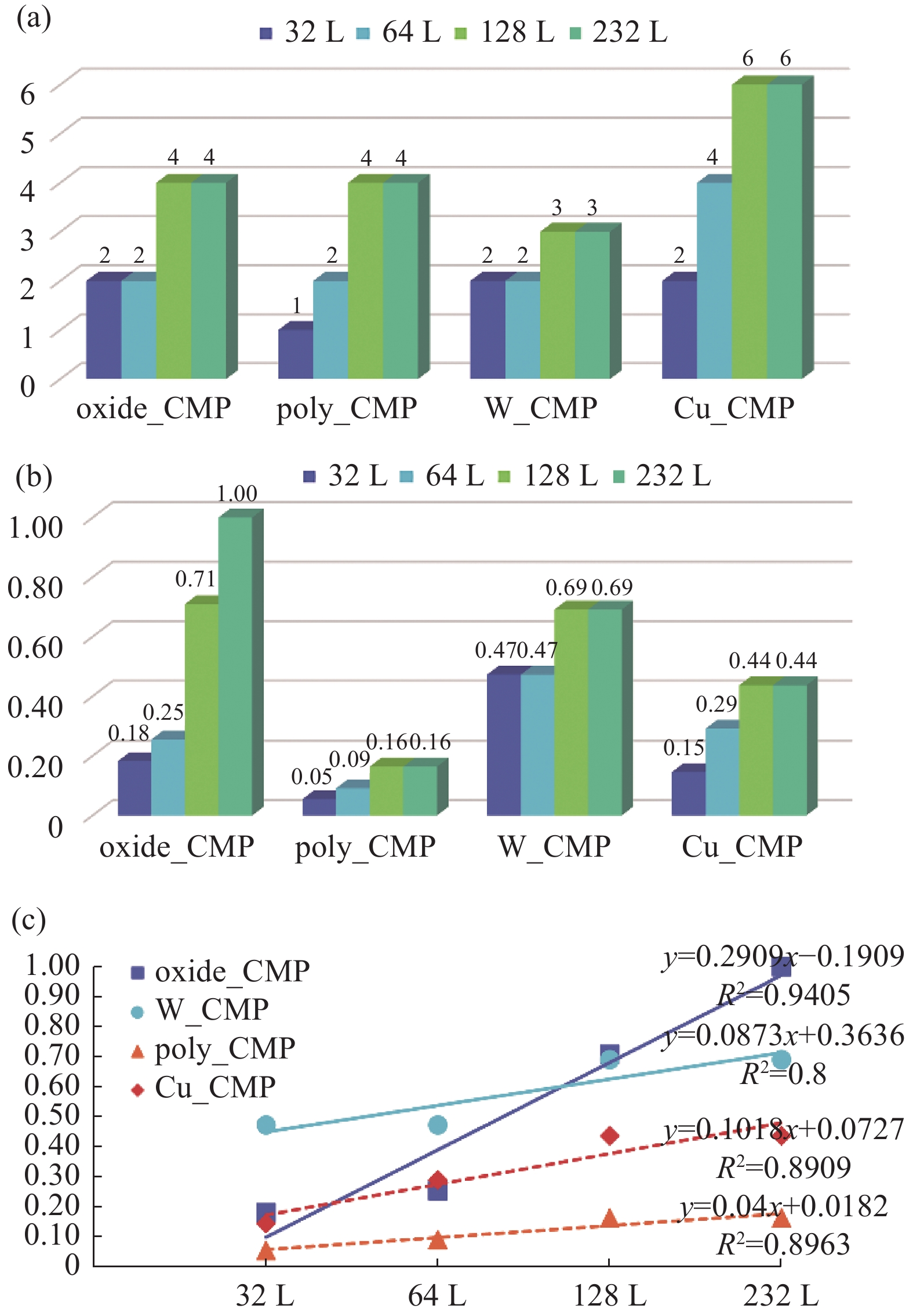

在制备Array存储单元时所包括的CMP制程有Oxide CMP、Poly CMP、W CMP和Cu CMP。在Array单元中,Oxide CMP和W CMP所移除的薄膜厚度为整个堆叠层的厚度,远大于在CMOS中的CMP移除量,所以在这两道制程中应使用高研磨速率的耗材配置。对于Poly CMP与Cu CMP制程,其通常是在形成堆叠存储单元之后,在上层作为导电互连结构,因此其研磨过程不涉及整个存储单元的厚度。如图7(a)和7(b)中所示,当堆叠层由32L到64L时,Oxide CMP和W CMP的工艺次数没有发生变化,Poly CMP与Cu CMP的工艺次数分别增加一倍,由于沉积的薄膜厚度加倍,在考虑到研磨速率没有变化的前提下,除了W CMP的设备数量不变,其余CMP工艺的设备数量均有所增加;当堆叠层由64L到128L时,由于一个128L的存储单元是由两个64L堆叠层叠加而成,因此四种CMP工艺次数同样也都有所增加,其中Oxide CMP和Poly CMP的工艺增加次数均为一倍,同时四种CMP工艺相对应的设备数量也都有不同程度的增加。当堆叠层由128L到232L时,由于同样采用“双堆栈”技术,所以使用的CMP工艺次数与128L时一样,没有发生变化,在CMP设备数量方面,由于只是每个stack的堆叠厚度增加,所以只有Oxide CMP的设备数量增加,而对于后段工艺Poly CMP、W CMP和Cu CMP的设备数量没有发生变化。如图7(c)中所示,对于Oxide CMP,其设备数量的增加随着技术节点的升级,呈现较为显著的正相关性,而对于Poly CMP、W CMP和Cu CMP,其在由32L到232L变化时正相关性不如Oxide CMP。

3.1. CMP设备的选型配置

3.2. 不同技术节点与CMP设备数量配置的关系

-

3D NAND存储芯片的快速发展,对其产线建设和产品质量都提出更高的要求,同时对制造过程中各工艺及设备配置问题也有着新的需求。本文以3D NAND X-tacking技术为基础,分析研究了某项目中CMP各工艺制程的特点和相应设备配置要点,从工艺流程、工艺设备选型和数量配置以及动力需求方面,研究了其与不同技术节点的对应关系。本研究对3D NAND项目的设备选型和数量配置提供理论依据和指导,对项目前期设计组线提供支撑。

随着技术与需求的发展,存储芯片势必会向着更高存储密度、更快写入擦除速度和更可靠稳定的方向发展,随之而来的是对制造过程中各工艺的更高质量需求。因此,对工艺及设备配置等相应工程化要点的研究,能够为实现产线高效稳定运行和产品高质量输出打下基础,其在存储芯片的发展中将扮演越来越重要的角色。

首页

首页 登录

登录 注册

注册

下载:

下载: