-

硅材料作为半导体产业的核心支柱,凭借其成熟的工艺技术和广泛的应用基础,推动了现代电子科技的飞速发展。当前,硅基半导体器件的制造精度已突破至纳米级别,并逐步向原子级精准制造迈进。比利时微电子研究中心(IMEC)于2022年发布了未来硅基晶体管的亚1纳米工艺节点路线图,指出到2036年,半导体器件将从纳米时代迈入原子(埃米)时代,这意味着硅材料的原子级精准制造将成为半导体科技发展的战略突破方向[1]。在这一进程中,光刻技术的升级扮演着至关重要的角色。光刻技术作为芯片制造的核心环节,其分辨率直接决定了半导体器件的制造精度。自20世纪70年代以来,光刻技术经历了显著的技术演进:从采用436 nm汞灯光源的接触式光刻,到使用365 nm波长的步进式光刻,再到基于193 nm波长的深紫外光刻技术,这一系列技术革新推动着芯片制程从微米级逐步升级到纳米级。然而,受限于瑞利衍射极限(R=k1λ/NA)的理论约束,193 nm光刻技术的加工精度被限制在32 nm线宽,已难以满足5 nm及以下技术节点芯片制造的精度需求[2]。为应对市场对高性能芯片的迫切需求,极紫外光刻(EUV,波长13.5 nm)技术应运而生。该技术通过极紫外光源、高数值孔径投影光学系统和先进的光刻胶材料,实现了13 nm线宽的加工精度,并预计在2028年左右突破 8 nm线宽精度,成为了5 nm及以下技术节点芯片制造中不可或缺的关键设备[3]。随着芯片制造技术迈入最先进的2 nm工艺节点,器件的特征尺寸已逐渐逼近原子尺度,传统光刻技术面临着衍射极限的严峻挑战。为突破这一困境,科研界正致力于探索超越经典光刻范式的新型光刻技术。

2022年,美国Zyvex公司推出基于扫描隧道显微镜(STM)的亚纳米分辨率光刻系统—ZyvexLitho1。该系统利用氢去钝化光刻技术(Hydrogen Depassivation Lithography,HDL),通过电子束移除硅表面氢原子,实现了世界上分辨率精度最高的0.768 nm分辨率的硅表面高精度图案化技术,远超现有极紫外光刻机的精度。HDL的核心原理是利用硅表面吸附的单层氢原子作为抗蚀剂,即硅表面经过氢钝化处理后,形成一层稳定的Si-H键,这层氢原子可以防止硅表面与外界环境发生反应。通过STM探针发射电子,可以在局部区域断裂Si-H键,使硅表面暴露出具有反应活性的硅悬键,从而实现原子级精度的图案化加工。这些暴露的区域可以用于后续的材料沉积、掺杂或蚀刻步骤,完成器件的制造。近年来,研究人员已成功利用HDL技术在硅基底上实现了单原子晶体管、量子逻辑门等传统光刻工艺无法企及的器件制造,为原子级精度的芯片制造和量子器件制造提供了重要的原理性验证。这些突破性成果不仅展示了HDL技术在原子尺度加工中的独特优势,也为未来半导体器件的微型化和高性能化开辟了全新的技术路径。随着HDL技术的不断成熟与优化,其加工效率、可靠性和可扩展性有望进一步提升,从而推动这些原型器件从实验室走向大规模制造。为了更直观地展示HDL技术的特点,表1从分辨率、加工精度、生产效率和适用场景等核心指标出发,系统地对比了HDL技术与当前业界广泛采用的其他光刻工艺的异同。通过表中的对比可见,HDL技术在加工分辨率、加工精度、掺杂控制(原位调控)等方面具有明显优势。然而,HDL技术也面临着生产效率较低且需在真空环境下封装等应用挑战。随着工艺的持续优化,预计在不久的将来,HDL技术有望在半导体芯片工艺升级、纳米压印技术升级和量子器件制造等前沿领域实现更广泛的应用,从而推动未来半导体科技的重大发展。

本文首先系统回顾了HDL技术的发展历程;随后,探讨了该技术在芯片制造工艺升级、纳米压印技术革新、量子计算等前沿领域的应用前景;最后,总结了当前面临的技术挑战,并对未来发展方向进行了展望。

-

HDL技术的诞生可以追溯到20世纪90年代对于STM纳米操纵技术的研究。1990年Eigler D M团队在镍表面用35个氙原子拼写“IBM”的创举,开启了原子尺度操控的新纪元[4]。在此技术背景下,NIST的Dagata J A等[5]于1991年率先在湿法钝化的Si(100)表面实现局域氧化图案,贝尔实验室Becker R S团队发现电子诱导氢脱附可形成清洁硅表面[6],IBM的Boland J J等[7]则通过热脱附研究揭示了单氢钝化表面的形成机制。这些关键突破为HDL的诞生奠定了基础。1993年,美国伊利诺伊大学研究团队首次报道了HDL技术。他们在氢钝化的Si(100)2×1重构表面,通过控制STM探针入射电子的剂量,实现了Si-H键的断裂,并观察到了两种不同的解吸附机制:(1)高偏压下的场发射电子解吸机制:在高电压下,STM探针发射的电子能量较高,能够直接断裂Si-H键;(2)低偏压下的多电子激发解吸机制:在低电压下,STM探针通过多个电子的非弹性散射过程激发Si-H键振动,间接断裂Si-H键[8]。Lyding J W等[9]研究了STM探针的电流和电压对氢去钝化精度的影响,发现低偏压(−4.5 V)和较高的隧穿电流(2 nA)能够实现原子级精细的光刻,同时有效减少STM针尖杂散电子引起的额外氢解吸。采用高偏压和低电流虽然会降低图案边缘的分辨率,但会提高整体解吸效率。基于这些发现,研究人员提出了一种分步优化策略:首先利用高偏压快速解吸微米级区域以提高加工效率,随后采用低偏压和较高电流对图案边缘进行精细修整,从而实现高效且原子级精确的光刻。而后,Zyvex Labs研究团队的Xu H等[10]进一步研究了氢去钝化过程中的参数(偏压、电流和电子剂量)对图案化精度的影响,给出了图案化参数的最佳范围。研究发现在最佳图案化参数(3 V,30 nA,10 mC cm−1)下,图形质量对STM针尖几何形状的依赖性显著降低,同时图形化精度始终保持在最高的双氢原子去除水平。基于这一发现,研究团队成功制备了宽度仅为0.768 nm的硅悬挂键纳米线。通过在相同区域内进行多次图案化,实现了不同图形之间亚1纳米精度的精确对准。这一发现证实了氢去钝化光刻技术具有优异的可重复性和工艺稳定性,为该技术在高精度纳米制造领域的实际应用提供了重要的理论依据和技术指导。

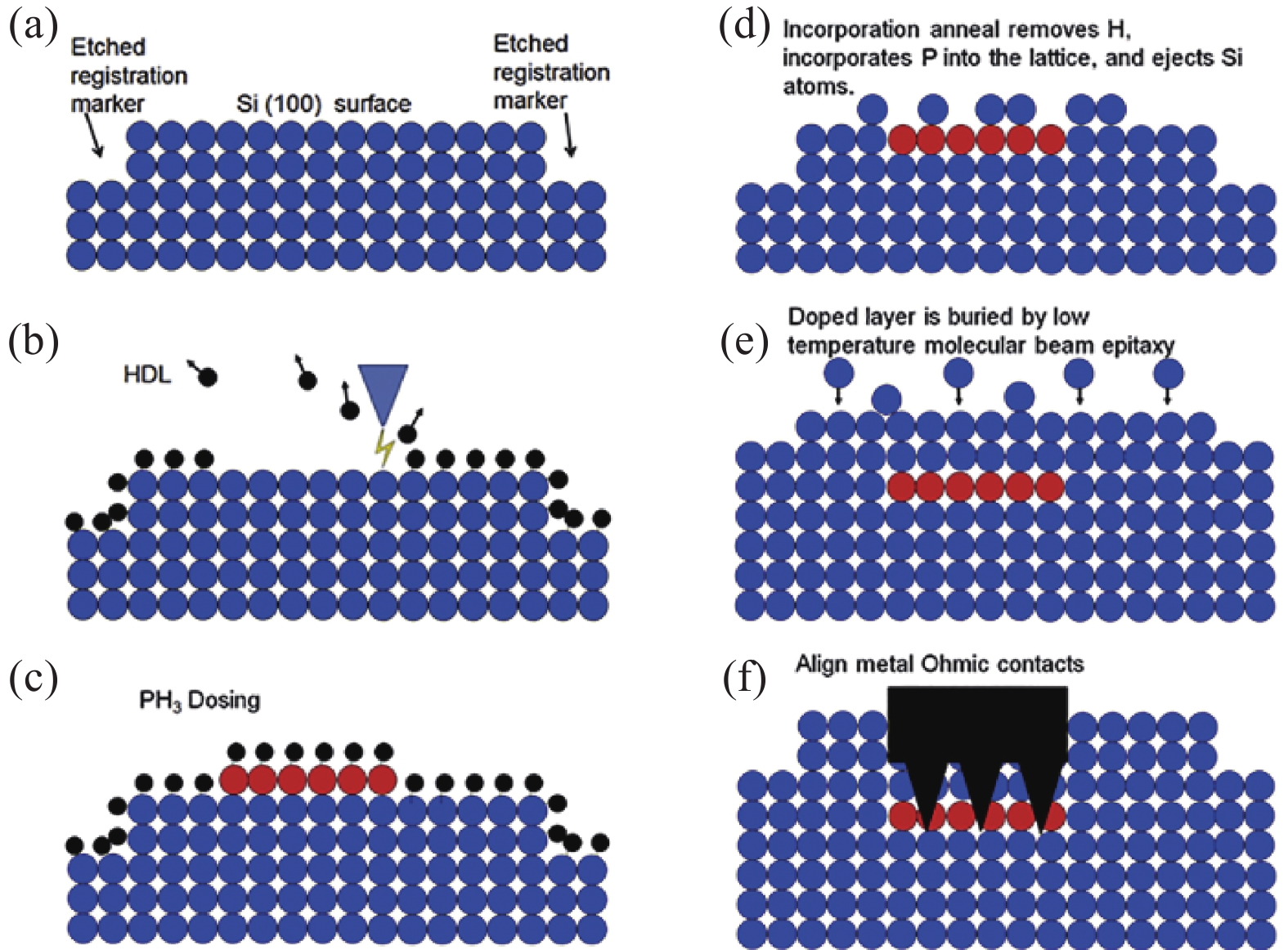

1990年代中期,Tucker J R和Shen T C[11]提出了利用氢去钝化技术制造纳米器件的初步设想。他们提出了一种分步制造方法(图1):(1)氢去钝化:利用STM探针在氢钝化的硅表面去除氢原子,暴露出硅悬键;(2)掺杂前驱体沉积:在暴露的硅悬键区域引入PH3、AsH3或B2H6等掺杂气体,形成有序排列的掺杂前驱体;(3)硅外延覆盖:通过低温硅外延技术覆盖硅层,限制掺杂原子的重新分布。(4)重复上述步骤以构建三维器件结构。在Tucker J R等[11]提出原子级器件制造的理论框架后,全球多个研究团队迅速跟进,展开了对氢去钝化工艺的开发与优化工作。其中,澳大利亚新南威尔士大学[12-27]以及美国Zyvex公司[10, 28-37]等研究机构率先在这一领域取得了重要进展。

-

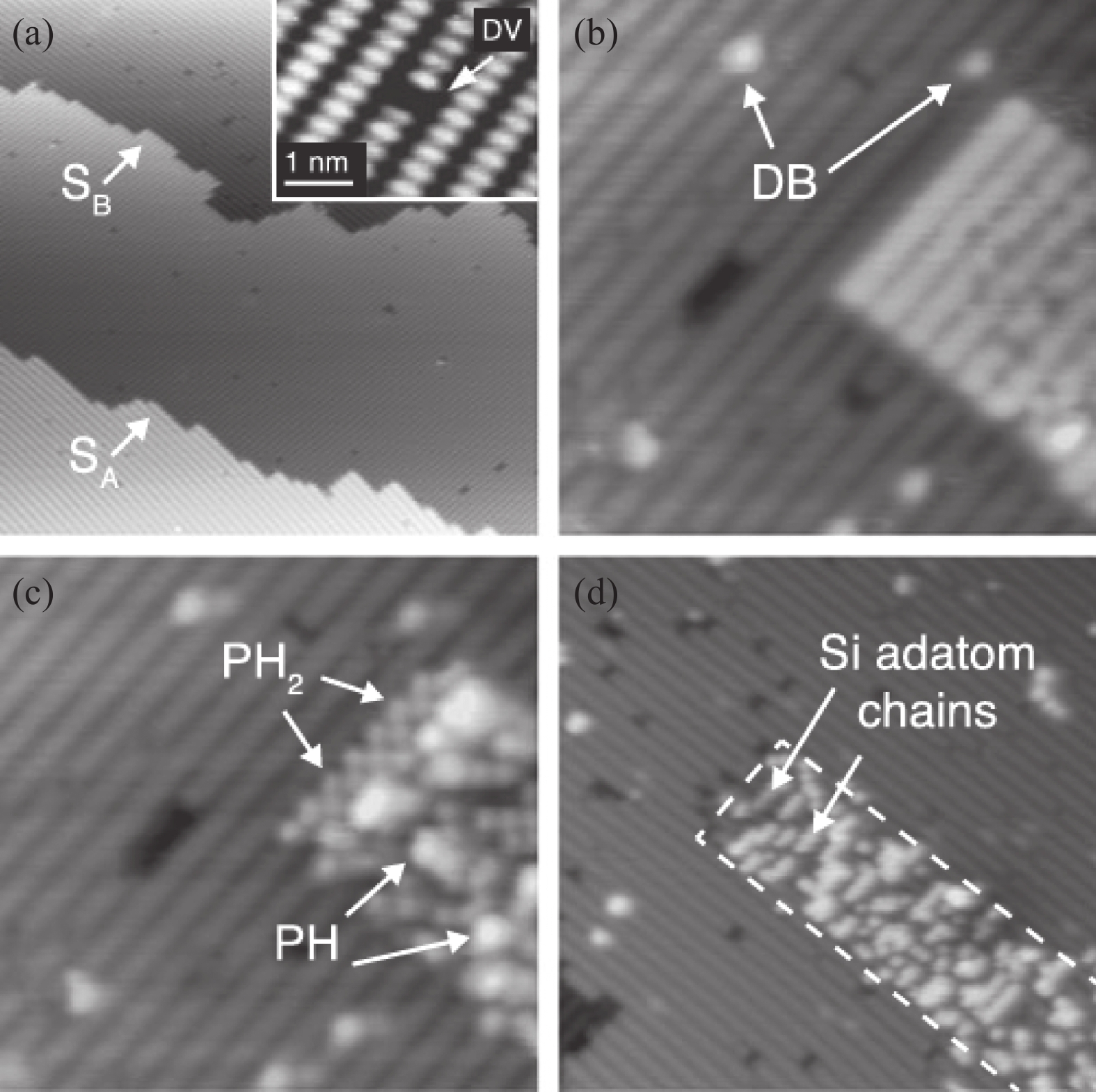

在通过STM光刻完成所需结构的图案化后,澳大利亚新南威尔士大学的Simmons M Y课题组开展了一系列在裸露硅区域进行受控掺杂的研究。2003年,他们率先展示了磷烷(PH3)可以在623 K的温和加热条件下将磷(P)原子掺入Si(001)表面,低于Si-H键分解温度(770 K),确保了氢去钝化模板在掺杂过程中保持完整。基于该技术,他们成功实现了以1 nm精度在硅中掺入单个P原子,并制造了宽度仅为4 nm的P原子掺杂纳米线[13]。 随后,该课题组进一步解析了PH3的掺杂过程:在氢钝化的硅表面(图2(a))上,利用HDL技术制备出图案化的硅悬键区域(图2(b)中长方形区域)。在PH3气氛中,PH3分子仅吸附在暴露的硅表面,而不会吸附在氢抗蚀层上(图2(c))。吸附后,PH3经历一系列连续解离,直到失去所有三个氢原子。具体过程如下:在PH3吸附的初始步骤中,PH3与硅表面形成配位键并立即解离为PH2 + H。随后,PH2片段在几分钟内进一步解离为PH + 2H。最终,PH片段解离生成P + 3H[16]。为了促进吸附的P原子掺入硅表面晶格,需要通过热激活使P原子取代硅原子,同时弹出一个硅原子。这些弹出的硅原子随后形成垂直于下方Si-P二聚体的一维链,这一现象标志着P原子的成功掺入(图2(d))。在掺杂剂成功掺入后,图案化区域随后被外延生长的约25 nm硅层覆盖,这一步骤的主要目的是:(1)完全激活掺杂剂,以及(2)消除表面缺陷对掺杂剂电子态的影响。尽管在硅封装过程中磷掺杂剂会向上偏析,但通过采用较低的硅外延生长温度(约250℃),偏析值可以被精确控制在6 Å的范围内[15, 38- 39]。这些研究系统地揭示了PH3在硅表面的解离、掺杂与封装机制,为下一步原子级精度半导体器件的制造提供了重要的技术基础。此外,基于HDL技术的硅表面砷(As)原子掺杂工艺也于近期取得了突破[40]。

在成功开发出完整的P原子掺杂策略后,研究人员利用该技术制备了不同宽度的P掺杂纳米导线,作为原子级器件的基本构建单元——电学引线。早期的研究表明,通过在暴露的硅表面进行饱和P原子掺杂(相当于1/4个单原子层),可以使相邻P原子之间的间距(约1 nm)小于其波尔半径(约2.5 nm),从而在掺杂区域产生金属导电性。这一理论很快在宽度从50 nm到90 nm不等的纳米导线上得到了实验验证[14, 41]。随后,研究人员将这一结论的适用范围进一步推广到1.5 nm(即4个硅原子)宽度的P掺杂纳米线上,并通过电学测量证明,即使在原子尺度下,这些纳米导线仍然表现出欧姆行为[21]。这些纳米导线具有高度平面化的特性,其导电范围仅跨越几个原子平面,从而实现了低至10−8 Ω·cm量级的二维电阻率。这种极低的电阻率对器件应用非常有利,不仅有助于避免测量期间的电阻加热效应,还能支持电信号的高速传输。

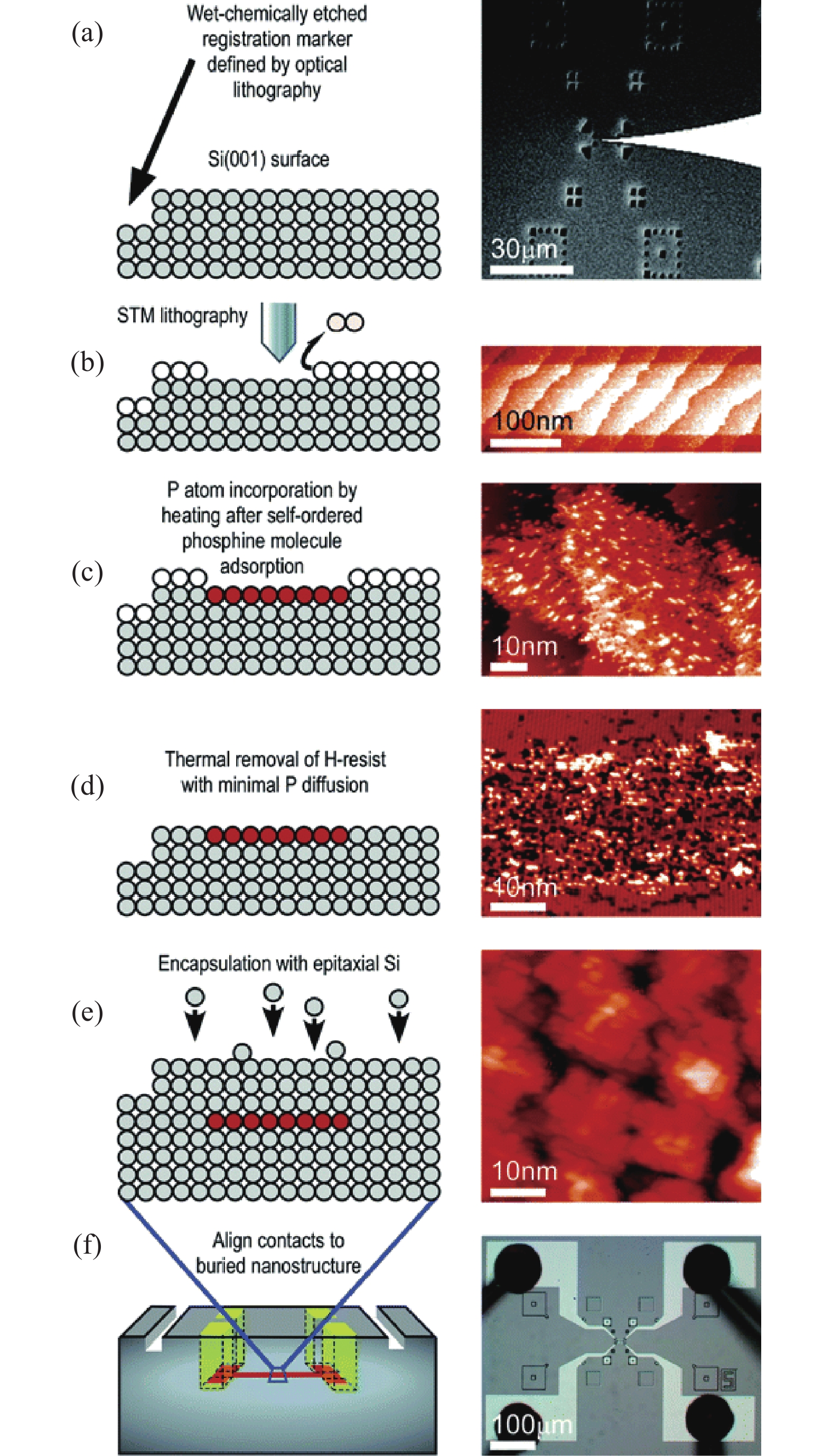

此外,为了解决HDL制造的原子尺度器件与外部世界连接的关键挑战,研究人员开发了一种定制设计的STM-SEM-MBE真空互联系统。该系统结合硅表面刻蚀出的对准标记和原子级精准的HDL光刻与磷原子掺杂工艺,成功实现了原子精度结构与微米尺度电极的高效连接(图3),为原子尺度器件的实用化铺平了道路[14, 17]。

-

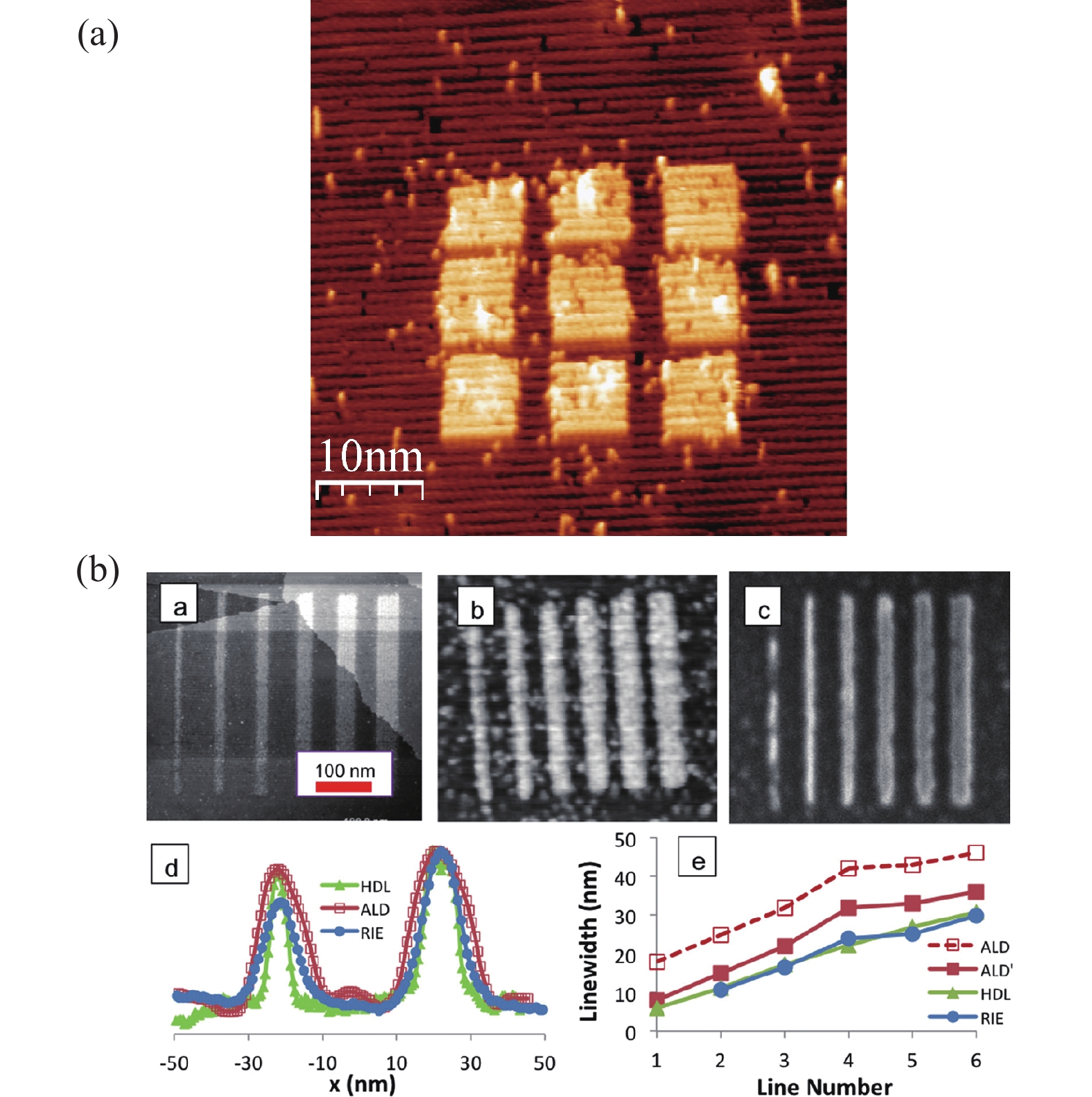

硅基芯片制造的前沿领域正朝着三维纳米结构的高精度制造方向快速发展。这一趋势在半导体芯片制造中尤为显著,器件结构从传统的二维平面型晶体管(Planar FET)逐步演进到三维的鳍式晶体管(FinFET),并进一步发展到当前的全环绕栅极晶体管(GAAFET)。此外,硅基三维纳米结构可以用于制造复杂的微机电系统(Micro-Electro-Mechanical Systems, MEMS)器件,如加速度计、陀螺仪和压力传感器,广泛应用于汽车、航空航天和消费电子领域。在这一背景下,HDL技术发展的另一个前沿方向是在硅基底上实现三维结构的原子精度制备。美国Zyvex公司在这一领域取得了突破性进展。2011年,Zyvex亚洲团队的Xu H等[30]首次提出利用HDL技术在Si(100)表面实现三维纳米结构的可控生长。他们通过HDL技术在氢钝化的Si(100)表面精确构建了具有原子级锐利边缘的硅悬挂键活性区域,并通过循环实施乙硅烷沉积与HDL技术,成功实现了三维纳米硅结构的区域选择性生长。实验结果表明,纳米结构的生长被严格限制在氢去钝化区域内(图4(a)),而氢终止的Si(100)表面则对前驱体分子表现出优异的抗吸附特性。这一发现为HDL技术在三维纳米结构制备中的应用提供了关键的原理性验证。2014年,Zyvex团队进一步优化了工艺流程,提出了创新的“HDL-ALD-RIE”三级联用技术:首先利用HDL技术在Si(100)表面暴露出活性区域,随后通过原子层沉积(ALD)技术在该区域制备二氧化钛(TiO2)硬掩膜,最后结合高精度反应离子刻蚀(RIE)工艺对无掩膜区域进行向下刻蚀。最终,他们成功实现了具有原子级锐利边缘、线宽低至6 nm、高度超过17 nm的三维纳米结构加工(图4(b))[34]。这些成果展现了HDL技术应用于硅基三维纳米结构制造中的巨大潜力。

-

氢去钝化光刻技术的发展面临的主要瓶颈之一是其较慢的图形化加工速度。针对如何提高氢去钝化效率(提升刻写速度)的问题,Zyvex公司的研究团队在2013年提出了多模态氢去钝化光刻(multimode HDL)的概念[33]。该技术通过结合高精度和高通量的光刻模式,显著提高了图案化效率。具体而言,对于大面积图案的中心部分,采用STM针尖场发射机理进行大线宽光刻(偏压约为8 V,束斑约为7 nm),而在需要原子级精度的区域则采用4−4.5 V的小偏压模式。实验结果表明,与单一模式的小偏压光刻相比,多模态技术的写入时间减少了78%,大幅提高了整体加工效率。

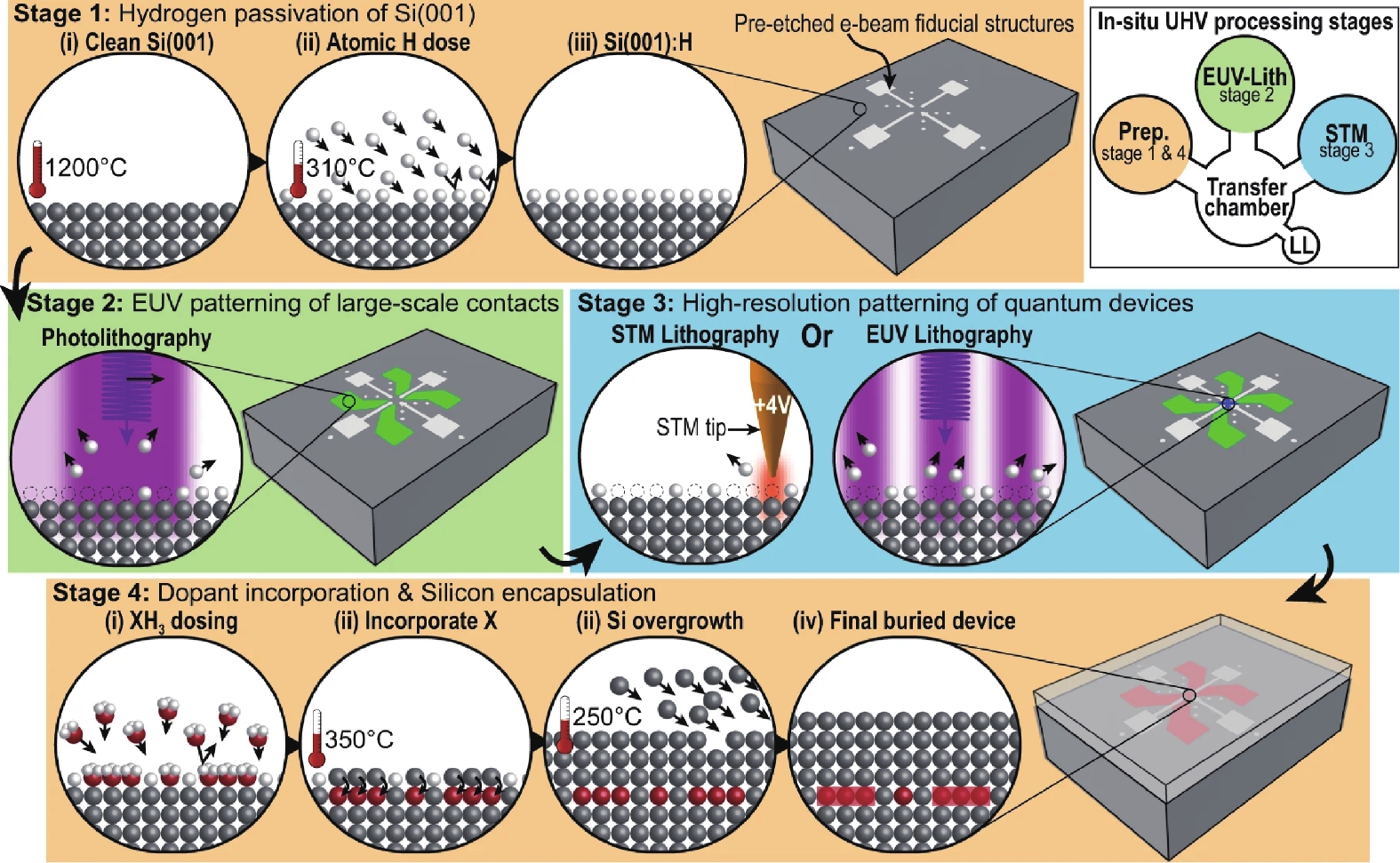

然而,完全基于STM针尖操纵的HDL光刻效率仍然明显低于电子束光刻和EUV光刻。这主要是因为STM的控制回路依赖于针尖电流的实时反馈来调节针尖与样品之间的距离,以防止针尖碰撞样品。当针尖速度接近1 μm/s时,这种控制回路可能会失效。为了进一步提高HDL光刻效率,英国伦敦大学学院和瑞士保罗谢勒研究所的联合团队提出了将EUV与STM相结合的多模态HDL光刻方案[43]。实验表明,在氢钝化的Si(100)表面,EUV光可以通过价带激发产生的二次电子诱导Si—H键断裂,从而实现氢去钝化,验证了利用光子实现氢去钝化的可行性。尽管该实验中使用的实验室EUV光源的氢去钝化效率较低,但作者提出,对于商用的300 W功率EUV光源,曝光时间可缩短至分钟量级,从而显著提高氢去钝化效率。通过整合EUV光刻的高通量和STM光刻的原子级精度,该技术不仅能够显著提升图案化效率,还能在关键区域保持极高的精度,为未来HDL技术的规模化应用提供了新的可能性(图5)。

-

限制氢去钝化加工效率的另一个瓶颈难题是STM的串行加工模式(即针尖一次只能移除一个氢原子),效率极低(仅约0.05 μm2/h)[35]。为突破这一瓶颈,Zyvex公司研究团队提出通过高度并行的STM探针阵列提升加工效率,利用多探针协同工作覆盖更大区域,从而显著提高加工通量[35]。传统的STM依赖于笨重的压电管进行纳米级定位,其带宽较低且易受蠕变和滞后效应的影响。基于MEMS的扫描器,其具有更小的质量和更高的带宽(可达10 kHz),能够实现更快的扫描速度。此外,MEMS探针的小尺寸和批量制造能力为构建多探针阵列提供了可能。为实现高效并行化,研究人员设计了基于微机电系统(MEMS)的三自由度(3 DoF)独立扫描器阵列。每个扫描器具备X、Y、Z方向的纳米级定位能力,通过局部控制器和全局总线架构实现分布式控制,有效减少了模拟信号串扰问题。与传统的并行电子束光刻不同,并行HDL的电子隧穿路径极短(仅数纳米),避免了库仑相互作用导致的束流畸变,使探针密度理论上可达每平方厘米10,000个以上。通过混合信号CMOS控制器和专用硬件设计,系统能够协调大规模探针阵列的动作,同时结合高精度漂移校正技术,确保各探针与硅表面二聚体行(dimer row)的原子级对准。最近,Zyvex公司团队对集成了Si探针的MEMS扫描器进行了测试,成功地在超高真空环境下实现原子级分辨率的成像,且扫描速度比传统STM快三倍,为未来实现高通量、并行化的STM平台奠定了基础[37]。未来,随着MEMS制造技术和控制算法的进步,并行HDL有望在加工效率、加工精度等方面实现突破,为原子级精密制造开辟新路径。

-

为了匹配多探针并行加工技术,制备能够在长时间扫描中保持加工质量的稳定探针是关键。然而,STM设备中常用的金属钨(W)或铂铱合金(Pt-Ir)探针由于化学活性较强,容易与样品表面作用引起针尖原子迁移或杂质吸附,导致探针稳定性下降,进而影响氢去钝化加工的精度。为了解决这一问题,研究者提出了使用金属性陶瓷材料作为替代方案,例如二硼化铪(HfB2)。二硼化铪不仅具有极高的硬度(非晶态下硬度可达20 GPa),还具备优异的化学稳定性和导电性,是一种理想的STM针尖材料[32]。通过化学气相沉积(CVD)技术,可以在钨针尖上沉积非晶态HfB2薄膜,形成W-HfB2复合探针。实验表明,这种复合探针在长时间扫描中表现出极高的稳定性,能够在数天内保持一致的成像质量,并且通过恒间距扫描隧道谱(STS)验证了其电子特性的高度一致性。因此,金属性陶瓷材料如HfB2为STM针尖的制备提供了一种创新解决方案,有效克服了传统探针材料在化学稳定性方面的局限性。

-

近年来,人工智能技术的快速发展为基于STM的氢去钝化技术的工艺智能化带来了前所未有的突破性机遇。通过深度学习算法对海量STM实验数据进行建模分析,研究人员能够构建针尖状态与操作参数之间的精确关联模型,从而智能预测最优加工条件,显著提升氢去钝化等基于原子级操控工艺的效率和稳定性。

近期,Krull A团队开发的DeepSPM人工智能框架实现了扫描探针显微镜(SPM)的全自动化操作[44]。该系统集成了集成智能区域选择、图像质量评估和针尖状态修复三大模块,结合卷积神经网络(Convolutional Neural Networks, CNN)与基于Q-learning的深度强化学习(Reinforcement Learning, RL)方法,在86 h内自动扫描超过1.2 μm2区域,生成16,000余张图像,并完成117次有效针尖修复与1,075次不良区域规避。实验表明,图像识别准确率达94%,针尖修复策略优于随机方法28%,显著提升了操作效率与数据质量。

在单原子操纵方面,Foster A S团队开发的深度强化学习STM操控系统同样展现出了卓越的性能[45]。该系统采用三项关键技术实现对金属表面吸附原子的亚纳米级精准操控:(1)结合CNN与电流信号经验公式,有效识别目标原子,减少约90%的冗余扫描;(2)结合匈牙利算法与快速探索随机树(Rapidly-exploring Random Tree, RRT),规划最优针尖移动路径;(3)改进Soft Actor-Critic(SAC)算法,仅需2000次训练迭代即可实现100%操作成功率,定位误差低至0.089 nm,并具备出色的自适应能力以应对针尖结构变化。

在自动化氢去钝化光刻技术研究方面,研究人员已开发出能够在H:Si(100)表面实现单氢原子精准去除的自动化程序[46]。该技术的核心创新在于引入基于STM电流信号的实时反馈控制机制,可精确检测氢原子脱附事件,并在脱附发生后快速调整成像参数。自动化的数据采集与分析也为后续基于深度学习的工艺优化奠定了坚实的基础。

这些前沿技术的融合应用为氢去钝化工艺的进一步优化开辟了新的技术路径。通过整合智能图像识别、实时反馈控制与针尖自适应操作算法,未来有望实现更加高效率且稳定的氢去钝化加工过程。

-

尽管氢去钝化技术能够实现原子级精度的图案化加工,但在实际操作过程中仍不可避免地会出现加工误差,例如在非目标区域错误地移除氢原子,从而导致结构失效或图案失真。为了解决这一问题,研究团队开发了一种基于STM的原位监测与修复技术—氢再钝化技术[47]。该技术利用STM对加工区域进行二次扫描,将目标图案与实际加工结果进行对比,能够实时识别并定位错误移除的氢原子。随后,通过将错误移除的氢原子重新附着到硅悬挂键上,恢复表面的氢钝化状态,从而修复错误结构。氢再钝化的具体步骤如下:首先,将STM尖端精确定位在目标悬挂键上方,关闭反馈控制以固定尖端高度;接着,调整偏压至100 mV至1.0 V之间,使针尖向样品表面移动500−800 pm,同时实时记录隧道电流的变化。研究人员发现,针尖上吸附的氢原子可以被转移到目标硅悬挂键上。成功的氢再钝化会伴随两种独特的隧道电流信号:type-I和type-II。type-I信号表现为隧道电流的突然增加,通常与针尖顶点的氢原子转移相关;type-II信号则表现为隧道电流的突然减少,通常与针尖非顶点的氢原子转移相关。这两种信号的出现表明氢原子已成功重新附着到悬挂键上,完成修复[47]。通过自动化程序,氢再钝化技术能够高效、精确地修复氢去钝化过程中产生的错误结构。这种原位修复技术确保了图案化区域的原子级精度,为原子尺度器件的开发和应用提供了重要的技术支持。

-

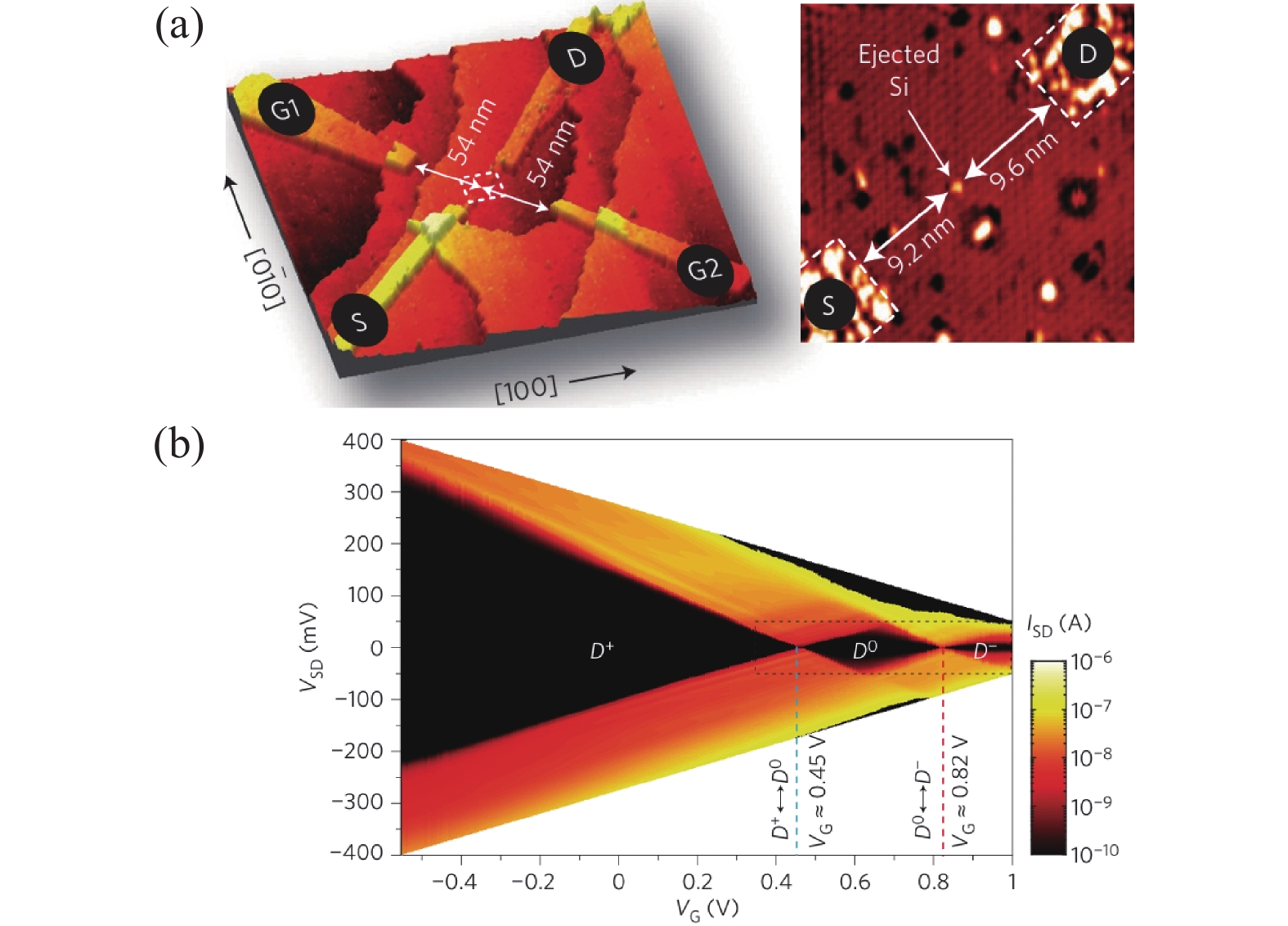

HDL技术为芯片制造工艺的突破性升级提供了原子级精度的技术路径,这种原子尺度操控能力为开发超高密度集成电路、单原子存储器和逻辑器件奠定了技术基础,推动芯片制造从纳米级向原子级跨越。2012年,澳大利亚新南威尔士大学的Simmons M Y团队展示了利用氢去钝化光刻技术制备的将单个P掺杂原子作为输运通道的单原子晶体管,展示了HDL技术在原子尺度上精确操控硅材料并构建功能器件的能力(图6)[22]。在单原子晶体管的制备过程中,研究人员首先使用STM在氢钝化的硅表面上定义出源极(S)、漏极(D)和栅极(G1、G2)的区域。通过选择性脱附氢原子,暴露出裸露的硅表面,随后引入磷化氢气体并进行热退火,使磷原子嵌入硅晶格中,形成高度磷掺杂的导电电极。通过精确控制脱附区域的大小和位置,研究人员能够将单个磷原子精确地放置在源极和漏极之间的通道中,形成单原子晶体管的核心结构。为了将磷原子封装在硅晶体中,研究人员在器件表面生长了一层约180 nm的外延硅层,将磷原子封装于硅晶体的体内,减少表面效应对其电子态的影响。

通过低温电子输运测量,研究人员观察到了P原子的离散量子能级,并验证了其电荷态的变化。实验测得单原子晶体管的充电能量(即D0和D−态之间的能量差)为47 ± 3 meV,与体材料硅中磷原子的充电能量(45.6 meV)非常接近。这表明,尽管磷原子位于高掺杂电极的附近,其电子态仍然保持了体相硅材料中单个掺杂原子的特性。通过调节栅极电压,研究人员能够精确控制磷原子的电荷态,实现从D+(正电荷态)到D0(中性态)再到D−(负电荷态)的转变。基于HDL技术制备的单原子晶体管标志着人类在半导体器件制造领域首次达到了摩尔定律的物理极限,即基于单个原子的器件,展示了在原子尺度上构建功能器件的可能性。这种原子级精度的制造技术为开发新一代高性能芯片提供了坚实的基础。例如,单原子存储器可以通过精确控制单个掺杂原子的电荷态来实现信息的存储与读取,而单原子逻辑门则可以利用单个原子的量子态进行逻辑运算,从而实现超高密度的集成电路。未来,通过提升HDL的加工效率与可靠性,该技术路径有望与极紫外光刻技术深度融合,进一步提升芯片制造的精度与效率,推动半导体科技实现突破性进展,并加速半导体芯片产业的全面升级。

-

随着半导体制造技术不断逼近物理极限,原子级精准的HDL技术有望成为下一代芯片制造的核心突破口。然而,尽管HDL技术在原子尺度器件的概念验证方面已经取得了显著成功,但要将其真正应用于工业化的芯片制造,必须解决其加工效率低的瓶颈难题。在这一背景下,Zyvex公司的研究团队指出,将HDL与技术应用于高精度纳米压印母版的制造有望为原子精度器件的规模化制造提供一条极具前景的技术路径[36]。作为极紫外光刻(EUV)的替代技术方案,纳米压印光刻近年来在微纳制造领域备受关注。其核心工艺借鉴了活字印刷原理:首先制备带有纳米图案的压印母版,通过机械压印将母版结构转印至旋涂于硅片的光刻胶层,随后利用紫外光固化或热固化技术固定图案,最终通过刻蚀工艺实现硅基底的图形化。目前该技术已在波导阵列、衍射光栅等光学元件制造中实现规模化应用,如Meta Quest Pro等头戴式设备的高分辨率显示模块便采用该工艺制造。值得注意的是,通过HDL技术制备具有原子级精度和大高宽比的三维结构,作为纳米压印母版,有望将压印线宽精度提升至6 nm[34],这或将实现纳米压印技术的精度升级,为该技术在半导体先进制程中的应用铺平道路。

-

1998年,Kane B E[48]提出了一种基于硅中掺杂P原子核自旋的硅基量子集成电路理论方案。该方案的核心是利用磷原子的自旋作为量子比特,理论上这些量子比特具有极长的相干时间,同时得益于硅基材料的良好可扩展性,该方案被认为在实现通用量子计算机方面具有巨大的潜力。然而,要实现这一方案,必须解决一个关键的技术挑战:制造高保真度(>99.9%)的单量子比特和双量子比特门。这需要实现原子级精度的掺杂控制,包括精确调控器件中磷原子的数量及其在硅晶格中的位置。这一技术要求远远超出了当时半导体加工工艺的能力范围。

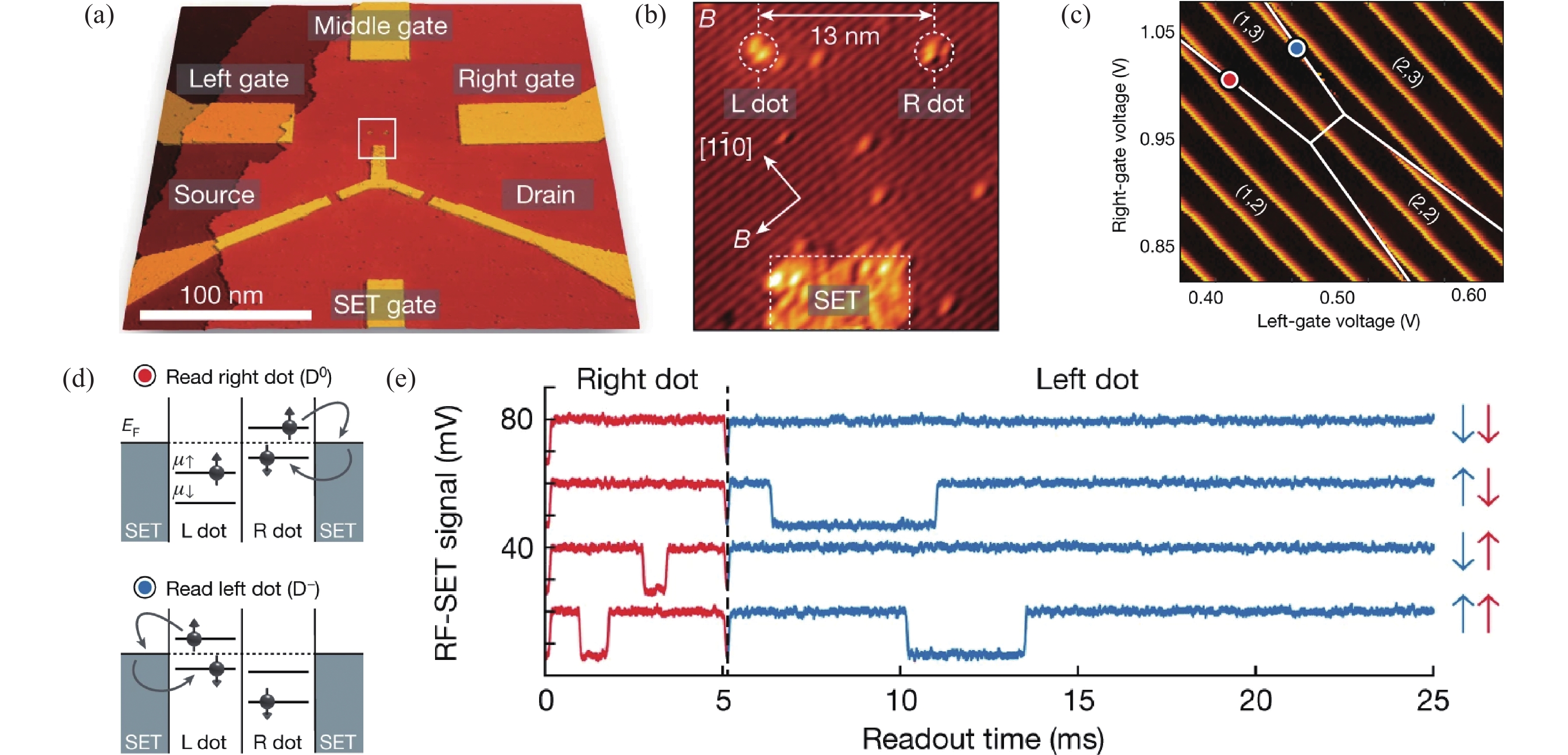

在氢去钝化光刻(HDL)技术发展的初期,研究人员便认识到利用HDL技术可以将掺杂磷原子以确定性的方式精确放置到硅晶体中,从而实现对量子比特特性的精确设计,以实现Kane B E等[49]的理论设想。随着HDL技术的不断发展,实现量子集成电路的关键技术逐渐取得突破。2017年,澳大利亚新南威尔士大学的Simmons M Y课题组利用其发展的基于HDL的平面器件制造技术,首次在硅中实现了精确放置的掺杂P原子量子比特,并利用单电子晶体管对其自旋态实现了高保真度(98.4±0.2%)读取[24]。随后,他们通过增加量子比特中的磷原子数量来增强电子约束,显著延长了量子点的电子自旋寿命,达到30 s,从而实现了对两个束缚在掺杂原子上的电子自旋量子比特的高保真度(99.8%)顺序读取[12]。2019年,他们进一步成功演示了基于掺杂P原子量子比特的高保真双量子比特门操作,标志着基于HDL技术制造可扩展通用量子计算机的关键组件已经完备[26]。最近,他们又实现了基于掺杂P原子的四量子比特的高保真度初始化和控制(图7)[27]。此外,HDL技术还支持在硅中进行三维制造,能够将多个器件层以纳米级精度堆叠和对齐在同一硅晶体中。这种三维制造能力不仅有助于实现低噪声量子比特门控和控制,还为全外延电子自旋共振(ESR)和核磁共振(NMR)天线、外延噪声屏蔽层以及片上集成量子集成电路的实现提供了可能性[25]。这些进展为未来大规模硅基量子集成电路的发展奠定了坚实的基础。

基于HDL技术实现的原子级精准P掺杂,也被用于构建二维或三维的量子点阵列,模拟复杂的多体物理系统,如扩展的费米-哈伯德模型[50]。通过精确控制量子点之间的距离和掺杂原子的数量,研究人员可以调节量子点之间的隧穿耦合强度和长程相互作用,从而模拟强关联电子系统中的金属−绝缘体转变、莫特绝缘体行为等现象。这种原子级精度的制造方法为研究拓扑相变、高温超导性等复杂量子现象提供了新的实验平台。

-

氢去钝化光刻技术作为原子级制造的突破性方法,成功将理查德·费曼于1959年提出的“我们能按需排列原子”("we can arrange the atoms the way we want")[51]的科学愿景转化为现实,展现出传统光刻技术难以企及的精度。其通过扫描隧道显微镜探针发射的电子束精确操控氢原子钝化层,实现了原子精度的图案化加工,显著提升了半导体器件的制造精度,为未来芯片技术迈向原子级精准制造提供了极具潜力的技术路径。在纳米压印制造方面,HDL技术也展现出了独特价值,通过原子层沉积与刻蚀工艺的协同,为纳米结构的大规模复制提供了原子级精度的三维压印母版。在量子信息领域,HDL已展现出革命性应用前景,既能精准控制单个磷原子构建量子比特,又可制备量子点结构探索量子现象。

不过,HDL技术要实现产业化应用仍需突破多重技术瓶颈。当前加工速度受限于探针人工操作模式,与半导体工业的规模化生产需求存在数量级差距,仍需人工智能辅助的自动化加工等方案提升效率。另外,在复杂量子器件的制造中,原子级误差的实时检测与动态补偿机制仍需完善,这对加工过程的控制系统提出了更高要求。此外,氢钝化工艺的稳定性、电子束参数的精准调控以及后续沉积/刻蚀工艺的协同优化,都需要建立更完备的理论模型和工艺标准。这些技术挑战的突破需要对表面物理化学过程的深入理解,以及跨学科的技术融合与创新。

氢去钝化光刻技术研究进展

Research Progress of Hydrogen Desorption Lithography Technology

-

摘要: 硅基半导体技术作为半导体产业的核心支柱,其制造精度已逼近几纳米,正向原子级精准制造迈进。然而,受瑞利衍射极限制约,传统的极紫外光刻技术已难以满足未来半导体制造对更高精度的需求。作为一种原子级精准的光刻技术,氢去钝化光刻(HDL)凭借其极高的空间分辨率和可扩展性,成为了突破硅基半导体技术发展瓶颈的重要战略方向。该技术基于扫描隧道显微镜探针的原子级操控,通过精确控制硅表面氢原子脱附,实现原子级图案化加工。自20世纪90年代问世以来,该技术已经成功制造出单原子晶体管、量子逻辑门等传统光刻工艺难以实现的器件,展现出了颠覆性的技术优势。文章系统回顾了HDL技术的发展历程与关键突破,并展望其未来发展方向。未来,通过进一步提升加工效率和可靠性,HDL技术有望在半导体芯片工艺升级、纳米压印技术升级和量子器件制造等前沿领域实现广泛的应用,推动未来半导体科技的重大发展。Abstract: Silicon-based semiconductor technology, as the cornerstone of the semiconductor industry, has achieved manufacturing precision at the scale of a few nanometers and is now advancing toward atomic-level precision. However, due to the Rayleigh diffraction limit, traditional extreme ultraviolet (EUV) lithography is unable to meet the demands for atomic-scale precision required in future semiconductor manufacturing. As an atomically precise lithography technique, hydrogen depassivation lithography (HDL) has emerged as a strategic solution to address this challenge, owing to its exceptional spatial resolution and scalability. Leveraging the atom manipulation capabilities of scanning tunneling microscope (STM), HDL enables atomic-scale patterning by precisely controlling the desorption of hydrogen atoms on silicon surfaces. Since its introduction in the 1990s, HDL has successfully fabricated devices such as single-atom transistors and quantum logic gates, which are unattainable through traditional lithography processes, showcasing its transformative advantages. This article provides a comprehensive review of the development history and key breakthroughs of HDL technology, while also exploring its future prospects. By further improving processing efficiency and reliability, HDL technology is poised to enable widespread applications in various fields, including semiconductor manufacturing, nanoimprint technology, and quantum device manufacturing, thereby driving significant progress in the future of semiconductor technology.

-

-

图 1 基于HDL技术的器件制造工艺[36]。(a)在超高真空腔体中对预先蚀刻出对准标记的硅表面进行高温清洁处理。(b)对清洁的硅表面进行氢钝化处理,并通过HDL技术暴露硅悬键,实现硅表面图案化。(c)向腔体中通入磷化氢气体,该气体将选择性吸附于暴露的硅悬键。(d)通过热处理将磷原子掺入硅晶格。(e)低温分子束外延生长硅层,实现掺杂磷原子的封装,形成埋入式器件。(f)对准标记并沉积金属化层,使其与埋入式器件的磷掺杂电极形成欧姆接触

Figure 1. Device fabrication process based on HDL technology[36]. (a) High-temperature cleaning of a pre-etched silicon surface with alignment markers in an ultra-high vacuum chamber. (b) Hydrogen passivation of the cleaned silicon surface, followed by HDL to expose silicon dangling bonds, enabling surface patterning. (c) Introduction of phosphine gas into the chamber, which selectively adsorbs onto the exposed silicon dangling bonds. (d) Incorporation of phosphorus atoms into the silicon lattice through thermal annealing. (e) Low-temperature molecular beam epitaxy growth of a silicon layer to encapsulate the doped phosphorus atoms, forming an embedded device. (f) Alignment of markers and deposition of a metallization layer to form ohmic contacts with the phosphorus-doped electrodes of the embedded device

图 2 基于HDL技术的硅表面磷原子精准掺杂工艺[42]。(a)清洁的Si(001)-2×1表面的STM图像,清晰地显示出两种类型的硅原子台阶。(b)Si(001)-2x1表面经过HDL光刻后形成的图案化区域(图像右下部分的长方形),显示出去钝化区域比周围氢终止区域的STM对比度更亮。同时,在附近可见非故意去钝化产生的单个硅悬挂键(dangling bond,DB)。(c)同一区域在磷化氢气体吸附后的图像。在去钝化区域内可以看到PH2和PH片段。(d)热处理激活磷原子掺杂后,掺杂区域表面形成了由磷置换出的硅原子所组成的原子链,表明磷原子已经成功掺入硅晶格

Figure 2. Precise phosphorus doping process on silicon surfaces based on HDL technology[42]. (a) STM image of a clean Si(001)-2×1 surface, showing two types of silicon atomic steps. (b) Patterned region (rectangular area in the image) formed on the Si(001)-2×1 surface after HDL lithography, displaying brighter STM contrast in the depassivated region compared to the surrounding hydrogen-terminated area. Additionally, single silicon dangling bonds (DB) is visible nearby. (c) Image of the same region after phosphine gas adsorption. PH2 and PH fragments can be observed within the depassivated region. (d) After thermal annealing to activate phosphorus doping, atomic chains composed of silicon atoms displaced by phosphorus are formed on the surface of the doped region, indicating successful incorporation of phosphorus atoms into the silicon lattice

图 3 原子精度器件与微米尺度电极的精准互连技术[14]。(左)(a)-(f)关键制造步骤的横截面示意图和最终器件的3D示意图。(右)对应的(a)STM针尖(白色)对准定位标记的SEM图像;(b)氢去钝化区域的STM图像;(c)-(d)氢抗蚀剂去除前和去除后的磷原子掺杂纳米线的STM图像;(e)硅外延生长后的STM图像;(f)最终器件的光学显微镜图像

Figure 3. Precise interconnection technology between atomic-scale devices and micron-scale electrodes[14]. (Left) (a)-(f) Cross-sectional schematics of key fabrication steps and a 3D illustration of the final device. (Right) Corresponding (a) SEM image of the STM tip (white) aligned with the alignment markers; (b) STM image of the hydrogen-depassivated region; (c)-(d) STM images of the phosphorus-doped nanowire before and after hydrogen resist removal; (e) STM image after silicon epitaxial growth; (f) Optical image of the final device

图 4 基于HDL技术的硅表面三维结构制造工艺。在HDL光刻制备的图案化硅表面,(a)通过硅低温外延生长实现三维硅结构的原子精度定向生长;(b)通过原子层沉积(ALD)的TiO2硬掩膜结合反应离子刻蚀(RIE),实现三维硅结构的原子精度定向刻蚀[34]

Figure 4. Fabrication process of three-dimensional silicon structures based on HDL technology. On the patterned silicon surface prepared by HDL lithography, (a) atomic-precision directional growth of three-dimensional silicon structures is achieved through low-temperature silicon epitaxial growth; (b) atomic-precision directional etching of three-dimensional silicon structures is realized using a TiO2 hard mask deposited by atomic layer deposition (ALD) combined with reactive ion etching (RIE)[34]

图 5 EUV-STM结合的多模态氢去钝化工艺示意图[43]。基于多模态氢去钝化光刻的器件制造主要分为四个阶段:阶段1,首先准备清洁的硅表面,随后对Si(001)进行氢钝化;阶段2,使用EUV氢去钝化光刻实现大尺度接触电极的图案化;阶段3,使用STM氢去钝化光刻在接触电极中心制作图案化的原子级精准结构;阶段4:进行磷原子的可控掺杂和硅外延生长封装,形成埋入式器件。之后,硅片被从超高真空腔中取出,沉积电极与埋入式器件形成欧姆接触

Figure 5. Schematic of the multi-modal hydrogen depassivation process combining EUV and STM[43]. The device fabrication based on multi-modal hydrogen depassivation lithography is divided into four stages. Stage 1: Preparation of a clean silicon surface, followed by hydrogen passivation of the Si(001) surface. Stage 2: Large-scale patterning of contact electrodes using EUV hydrogen depassivation lithography. Stage 3: Fabrication of atomically precise patterned structures at the center of the contact electrodes using STM hydrogen depassivation lithography. Stage 4: Controlled doping of phosphorus atoms and encapsulation through silicon epitaxial growth to form embedded devices. Subsequently, the silicon wafer is taken out from the ultra-high vacuum chamber, and electrodes are deposited to form ohmic contacts with the embedded devices

图 6 氢去钝化光刻技术制造的硅基单原子晶体管[22]。(a) 单原子晶体管的三维和平面STM图像。(b)器件的源漏电流(以对数刻度表示)随源漏偏压(VSD)和栅极电压(VG)的变化。其中,掺杂原子(Donor,D)的电荷态经历了D+向D0和D−的连续转变,对应的栅极电压分别为0.45 V和0.82 V

Figure 6. Silicon-based single-atom transistor fabricated using hydrogen depassivation lithography (HDL)[22]. (a) Three-dimensional and planar STM images of the single-atom transistor. (b) Source-drain current (plotted on a logarithmic scale) as a function of source-drain bias (VSD) and gate voltage (VG). The charge state of the dopant atom (Donor, D) undergoes a continuous transition from D+ to D0 to D−, with corresponding gate voltages of 0.45 V and 0.82 V, respectively

图 7 高保真、独立读取的掺杂原子两比特门[26]。(a)两个量子比特器件的STM图像。较亮的区域为氢去钝化光刻形成的图案化区域。该器件由四个栅极组成:左栅极、中间栅极、右栅极以及用于控制量子比特和射频单电子晶体管(RF-SET)电化学势的SET栅极。(b)RF-SET和定义量子比特L(左)和R(右)的两个掺杂量子点的STM图像。(c)RF-SET的反射振幅对于左栅极和右栅极电压的函数,图中标明了电子数(nL,nR)。白线表示单个量子比特与RF-SET之间的电荷跃迁。蓝点和红点分别标记了在左量子比特和右量子比特上进行自旋读取的位置。(d)两个量子比特的电化学势μ↑和μ↓(分别对应自旋态∣↑

$\rangle $ 和∣↓$\rangle $ ),展示了如何使用能量选择协议测量电子自旋态。(e)基于时序测量的RF-SET反射振幅,用于区分四种可能的量子比特状态Figure 7. High-fidelity, independent single-shot spin readout of two donor qubits[26]. (a) STM micrograph of the two-qubit device. The lighter regions show the open lithographic hydrogen mask. The device consists of four gates: left, middle, right and the SET gate used to control the electrochemical potentials of the qubits and the RF-SET. (b) Close-up STM micrograph of the RF-SET and the two donor dots that define the qubits L (left) and R (right). (c) Reflected amplitude of the RF-SET as a function of the left- and right-gate voltages with electron numbers (nL, nR). The white lines indicate charge transitions between individual qubits and the RF-SET. The blue and red dots mark the position where spin readout is performed on the left and right qubit, respectively. (d) Electrochemical potentials μ↑ and μ↓ of the two qubits (with spin ∣↑

$\rangle $ and ∣↓$\rangle $ , respectively, showing how the electron spin states are measured using an energy-selective protocol. (e) Reflected RF-SET amplitude measured as a function of time, used to distinguish between the four possible qubit states表 1 不同光刻技术实现路径对比分析

Table 1. Comparison of Different Lithography Technologies

技术参数 氢去钝化光刻

( HDL)极紫外光刻

(EUV)电子束光刻

( EBL)纳米压印光刻

( NIL)加工分辨率 0.768 nm 8 nm 5−10 nm 10−20 nm 掺杂控制 原位调控 需后续离子注入 需后续离子注入 需后续离子注入 图案稳定性 采用氢抗蚀剂,仅在真空中

稳定,需原位封装采用光敏感聚合物,

稳定性高采用电子敏感聚合物,

稳定性高采用光或热敏感聚合物,

稳定性高加工精度 原子级平滑 受成像误差、光学畸变

等影响,纳米级受电子散射影响,纳米级 受模板质量影响,纳米级 生产效率 低(串行写入) 高(并行曝光) 较低(串行写入) 高(并行压印) 适用场景 自由度高,适用于原子级、

量子器件芯片大规模制造 自由度高,适合定制化器件 周期性结构

(光栅、存储器件)产业化成熟度 实验室阶段 行业主流 研发/掩膜版加工 小规模量产 -

[1] Imec. Smaller, better, faster: imec presents chip scaling roadmap[EB/OL]. https://www.imec-int.com/en/articles/smaller-better-faster-imec-presents-chip-scaling-roadmap 2023 [2] Yang D K, Wang D, Huang Q S, et al. The development of laser-produced plasma EUV light source[J]. Chip, 2022, 1(3): 100019 doi: 10.1016/j.chip.2022.100019 [3] Van Schoot J, van Setten E, Troost K, et al. High-NA EUV lithography exposure tool: program progress[C]//Proceedings of Extreme Ultraviolet (EUV) Lithography XI, San Jose: SPIE, 2020: 1132307 [4] Eigler D M, Schweizer E K. Positioning single atoms with a scanning tunnelling microscope[J]. Nature, 1990, 344(6266): 524−526 doi: 10.1038/344524a0 [5] Dagata J A, Schneir J, Harary H H, et al. Pattern generation on semiconductor surfaces by a scanning tunneling microscope operating in air[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 1991, 9(2): 1384−1388 [6] Becker R S, Higashi G S, Chabal Y J, et al. Atomic-scale conversion of clean Si(111): H-1×1 to Si(111)-2×1 by electron-stimulated desorption[J]. Physical Review Letters, 1990, 65(15): 1917−1920 doi: 10.1103/PhysRevLett.65.1917 [7] Boland J J, Parsons G N. Bond selectivity in silicon film growth[J]. Science, 1992, 256(5061): 1304−1306 doi: 10.1126/science.256.5061.1304 [8] Shen T C, Wang C, Abeln G C, et al. Atomic-scale desorption through electronic and vibrational excitation mechanisms[J]. Science, 1995, 268(5217): 1590−1592 doi: 10.1126/science.268.5217.1590 [9] Lyding J W, Shen T C, Abeln G C, et al. Nanoscale patterning and selective chemistry of silicon surfaces by ultrahigh-vacuum scanning tunneling microscopy[J]. Nanotechnology, 1996, 7(2): 128−133 doi: 10.1088/0957-4484/7/2/006 [10] Chen S, Xu H, Goh K E J, et al. Patterning of sub-1 nm dangling-bond lines with atomic precision alignment on H: Si(100) surface at room temperature[J]. Nanotechnology, 2012, 23(27): 275301 doi: 10.1088/0957-4484/23/27/275301 [11] Tucker J R, Shen T C. Prospects for atomically ordered device structures based on STM lithography[J]. Solid-State Electronics, 1998, 42(7-8): 1061−1067 doi: 10.1016/S0038-1101(97)00302-X [12] Watson T F, Weber B, Hsueh Y L, et al. Atomically engineered electron spin lifetimes of 30 s in silicon[J]. Science Advances, 2017, 3(3): e1602811 doi: 10.1126/sciadv.1602811 [13] Schofield S R, Curson N J, Simmons M Y, et al. Atomically precise placement of single dopants in Si[J]. Physical Review Letters, 2003, 91(13): 136104 doi: 10.1103/PhysRevLett.91.136104 [14] Ruess F J, Oberbeck L, Simmons M Y, et al. Toward atomic-scale device fabrication in silicon using scanning probe microscopy[J]. Nano Letters, 2004, 4(10): 1969−1973 doi: 10.1021/nl048808v [15] Oberbeck L, Curson N J, Hallam T, et al. Measurement of phosphorus segregation in silicon at the atomic scale using scanning tunneling microscopy[J]. Applied Physics Letters, 2004, 85(8): 1359−1361 doi: 10.1063/1.1784881 [16] Wilson H F, Warschkow O, Marks N A, et al. Phosphine dissociation on the Si(001) surface[J]. Physical Review Letters, 2004, 93(22): 226102 doi: 10.1103/PhysRevLett.93.226102 [17] Rueß F J, Oberbeck L, Goh K E J, et al. The use of etched registration markers to make four-terminal electrical contacts to STM-patterned nanostructures[J]. Nanotechnology, 2005, 16(10): 2446−2449 doi: 10.1088/0957-4484/16/10/076 [18] Wilson H F, Warschkow O, Marks N A, et al. Thermal dissociation and desorption of PH3 on Si(001): a reinterpretation of spectroscopic data[J]. Physical Review B, 2006, 74(19): 195310 doi: 10.1103/PhysRevB.74.195310 [19] Rueß F J, Pok W, Reusch T C G, et al. Realization of atomically controlled dopant devices in silicon[J]. Small, 2007, 3(4): 563−567 doi: 10.1002/smll.200600680 [20] Fuechsle M, Rueß F J, Reusch T C G, et al. Surface gate and contact alignment for buried, atomically precise scanning tunneling microscopy–patterned devices[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2007, 25(6): 2562−2567 [21] Weber B, Mahapatra S, Ryu H, et al. Ohm’s law survives to the atomic scale[J]. Science, 2012, 335(6064): 64−67 doi: 10.1126/science.1214319 [22] Fuechsle M, Miwa J A, Mahapatra S, et al. A single-atom transistor[J]. Nature Nanotechnology, 2012, 7(4): 242−246 doi: 10.1038/nnano.2012.21 [23] Warschkow O, Curson N J, Schofield S R, et al. Reaction paths of phosphine dissociation on silicon (001)[J]. The Journal of Chemical Physics, 2016, 144(1): 014705 doi: 10.1063/1.4939124 [24] Broome M A, Watson T F, Keith D, et al. High-fidelity single-shot singlet-triplet readout of precision-placed donors in silicon[J]. Physical Review Letters, 2017, 119(4): 046802 doi: 10.1103/PhysRevLett.119.046802 [25] Koch M, Keizer J G, Pakkiam P, et al. Spin read-out in atomic qubits in an all-epitaxial three-dimensional transistor[J]. Nature Nanotechnology, 2019, 14(2): 137−140 doi: 10.1038/s41565-018-0338-1 [26] He Y, Gorman S K, Keith D, et al. A two-qubit gate between phosphorus donor electrons in silicon[J]. Nature, 2019, 571(7765): 371−375 doi: 10.1038/s41586-019-1381-2 [27] Reiner J, Chung Y, Misha S H, et al. High-fidelity initialization and control of electron and nuclear spins in a four-qubit register[J]. Nature Nanotechnology, 2024, 19(5): 605−611 doi: 10.1038/s41565-023-01596-9 [28] Randall J N, Lyding J W, Schmucker S, et al. Atomic precision lithography on Si[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2009, 27(6): 2764-2768 [29] Randall J N, Ballard J B, Lyding J W, et al. Atomic precision patterning on Si: an opportunity for a digitized process[J]. Microelectronic Engineering, 2010, 87(5-8): 955−958 doi: 10.1016/j.mee.2009.11.143 [30] Goh K E J, Chen S, Xu H, et al. Using patterned H-resist for controlled three-dimensional growth of nanostructures[J]. Applied Physics Letters, 2011, 98(16): 163102 doi: 10.1063/1.3582241 [31] Randall J N, Von Her J R, Ballard J, et al. Atomically precise manufacturing: the opportunity, challenges, and impact, atomic scale interconnection machines[M]//Joachim C. Atomic scale interconnection machines. Berlin, Heidelberg: Springer, 2012: 89−106 [32] Schmucker S W, Kumar N, Abelson J R, et al. Field-directed sputter sharpening for tailored probe materials and atomic-scale lithography[J]. Nature Communications, 2012, 3(1): 935 doi: 10.1038/ncomms1907 [33] Ballard J B, Sisson T W, Owen J H G, et al. Multimode hydrogen depassivation lithography: a method for optimizing atomically precise write times[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2013, 31(6): 06FC01 [34] Ballard J B, Owen J H G, Owen W, et al. Pattern transfer of hydrogen depassivation lithography patterns into silicon with atomically traceable placement and size control[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2014, 32(4): 041804 [35] Randall J N, Owen J H G, Lake J, et al. Highly parallel scanning tunneling microscope based hydrogen depassivation lithography[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2018, 36(6): 06JL05 [36] Randall J N, Owen J H G, Fuchs E, et al. Digital atomic scale fabrication an inverse Moore's Law – a path to atomically precise manufacturing[J]. Micro and Nano Engineering, 2018, 1: 1−14 doi: 10.1016/j.mne.2018.11.001 [37] Alipour A, Fowler E L, Moheimani S O R, et al. Atom-resolved imaging with a silicon tip integrated into an on-chip scanning tunneling microscope[J]. Review of Scientific Instruments, 2024, 95(3): 033703 doi: 10.1063/5.0180777 [38] Oberbeck L, Curson N J, Simmons M Y, et al. Encapsulation of phosphorus dopants in silicon for the fabrication of a quantum computer[J]. Applied Physics Letters, 2002, 81(17): 3197−3199 doi: 10.1063/1.1516859 [39] Goh K E J, Oberbeck L, Simmons M Y, et al. Effect of encapsulation temperature on Si: P δ-doped layers[J]. Applied Physics Letters, 2004, 85(21): 4953−4955 doi: 10.1063/1.1827940 [40] Stock T J Z, Warschkow O, Constantinou P C, et al. Atomic-scale patterning of arsenic in silicon by scanning tunneling microscopy[J]. ACS Nano, 2020, 14(3): 3316−3327 doi: 10.1021/acsnano.9b08943 [41] Shen T C, Kline J S, Schenkel T, et al. Nanoscale electronics based on two-dimensional dopant patterns in silicon[J]. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 2004, 22(6): 3182−3185. [42] Miwa J A, Simmons M Y. Atomic-scale devices in silicon by scanning tunneling microscopy[M]//Joachim C. Atomic scale interconnection machines. Berlin, Heidelberg: Springer, 2012: 181−196 [43] Constantinou P, Stock T J Z, Tseng L T, et al. EUV-induced hydrogen desorption as a step towards large-scale silicon quantum device patterning[J]. Nature Communications, 2024, 15(1): 694 doi: 10.1038/s41467-024-44790-6 [44] Krull A, Hirsch P, Rother C, et al. Artificial-intelligence-driven scanning probe microscopy[J]. Communications Physics, 2020, 3(1): 54 doi: 10.1038/s42005-020-0317-3 [45] Chen I J, Aapro M, Kipnis A, et al. Precise atom manipulation through deep reinforcement learning[J]. Nature Communications, 2022, 13(1): 7499 doi: 10.1038/s41467-022-35149-w [46] Møller M, Jarvis S P, Guérinet L, et al. Automated extraction of single H atoms with STM: tip state dependency[J]. Nanotechnology, 2017, 28(7): 075302 doi: 10.1088/1361-6528/28/7/075302 [47] Achal R, Rashidi M, Croshaw J, et al. Lithography for robust and editable atomic-scale silicon devices and memories[J]. Nature Communications, 2018, 9(1): 2778 doi: 10.1038/s41467-018-05171-y [48] Kane B E. A silicon-based nuclear spin quantum computer[J]. Nature, 1998, 393(6681): 133−137 doi: 10.1038/30156 [49] O’Brien J L, Schofield S R, Simmons M Y, et al. Towards the fabrication of phosphorus qubits for a silicon quantum computer[J]. Physical Review B, 2001, 64(16): 161401 doi: 10.1103/PhysRevB.64.161401 [50] Wang X Q, Khatami E, Fei F, et al. Experimental realization of an extended Fermi-Hubbard model using a 2D lattice of dopant-based quantum dots[J]. Nature Communications, 2022, 13(1): 6824 doi: 10.1038/s41467-022-34220-w [51] Feynman R P. There’s plenty of room at the bottom[J]. Resonance, 2011, 16(9): 890−905 doi: 10.1007/s12045-011-0109-x -

首页

首页 登录

登录 注册

注册

下载:

下载: