-

提升硅基晶体管器件的能效是集成电路的核心[1-3], 使用具有更高载流子迁移率且与硅兼容的SiGe材料是提升器件能效的重要方法[4,5]. 目前, 基于硅上应力弛豫的SiGe薄膜及该衬底上的应变Si技术已经在高性能电子器件[6,7]、光电子器件[8,9]、量子信息器件[10-12]和神经形态器件[13]等领域得到广泛应用.

传统的SiGe薄膜材料主要通过在Si(001)衬底上直接外延生长制备, 该过程涉及失配应力的累积以及通过产生位错来释放应力. 因此, 直接在Si上生长SiGe薄膜不可避免会产生大量的穿透位错, 密度通常在107—1010 cm–2量级[14]. 为了提高外延SiGe薄膜的质量, 研究人员提出两种生长缓冲层的方法. 第一种是外延生长Si/SiGe超晶格缓冲层, 这种结构能够有效地改变薄膜中的应力分布, 从而改变位错的传播方向, 且在外延层中Ge含量较高的情况下, 表面依然能够保持较好的平整性, 显著减少穿透位错密度[15,16]. 1992年, IBM实验室利用超高真空化学气相沉积(UHV-CVD)生长Si/SiGe超晶格缓冲层, 成功将穿透位错密度降低至107 cm–2量级[17]. 另一种方法是在生长SiGe缓冲层时逐渐增加Ge的含量, 但需要生长微米级厚度的薄膜, 且过厚的缓冲层中的位错堆积还将导致大的表面粗糙度[18]. 1991年, 贝尔实验室采用分子束外延(MBE)生长Ge组分渐变层, 将穿透位错密度降至106 cm–2量级, 但表面出现了严重的交叉线(crosshatch)结构[19].

尽管缓冲层技术大幅提高了SiGe薄膜的质量, 但还存在105—108 cm–2的穿透位错密度[20]. 应变不均匀、穿透位错、交叉线等缺陷会降低薄膜中载流子的迁移率, 影响器件性能[21]. 为了避免晶格失配带来的缺陷, 2011年美国威斯康辛大学Lagally课题组[22,23]提出在绝缘体上硅(SOI)衬底上外延、腐蚀剥离和转移至硅衬底以获得应力弛豫SiGe纳米薄膜(SiGe NM)的方法. 但其制备的SiGe纳米薄膜存在尺寸小(1 mm × 1 mm)、褶皱多、表面粗糙度大(0.6—0.7 nm)等问题, 且在腐蚀中使用了氢氧化钾(KOH)溶液, 可能会对器件带来钾离子污染. 本研究利用湿法刻蚀SOI上的牺牲层和异质结中的上下硅层, 成功实现了更大尺寸、低褶皱、高平整度且无金属离子污染的Si(001)衬底上应力弛豫的单晶SiGe纳米薄膜. 首先在SOI衬底(001)上通过MBE制备上下Si层厚度相同的Si/SiGe/Si异质结, SiGe层的厚度低于产生位错的临界厚度[24]. 然后选择性刻蚀SiO2将异质结从SOI衬底上剥离, 再选择性刻蚀异质结中的上下Si层, 使应变的SiGe薄膜中的应力弛豫, 最后成功将该纳米薄膜转移至Si(001)衬底. 进一步在该应力弛豫的SiGe薄膜上外延制备了高质量的SiGe/Si/SiGe异质结.

本研究使用拉曼光谱(Raman)分析异质结中的应力情况, 利用原子力显微镜(AFM)表征薄膜的表面形貌, 利用电子通道衬度成像(ECCI)和球差校正透射电子显微镜(AC-TEM)分析表征薄膜的表面和界面性能. 研究表明, 制备的SiGe薄膜中的应力完全弛豫, Si/SiGe异质结薄膜的表面粗糙度仅0.118 nm, 转移薄膜上外延的异质结中没有位错. 研究工作对提升Ⅳ族异质材料的载流子迁移率, 实现高性能硅基自旋量子比特具有重要意义.

-

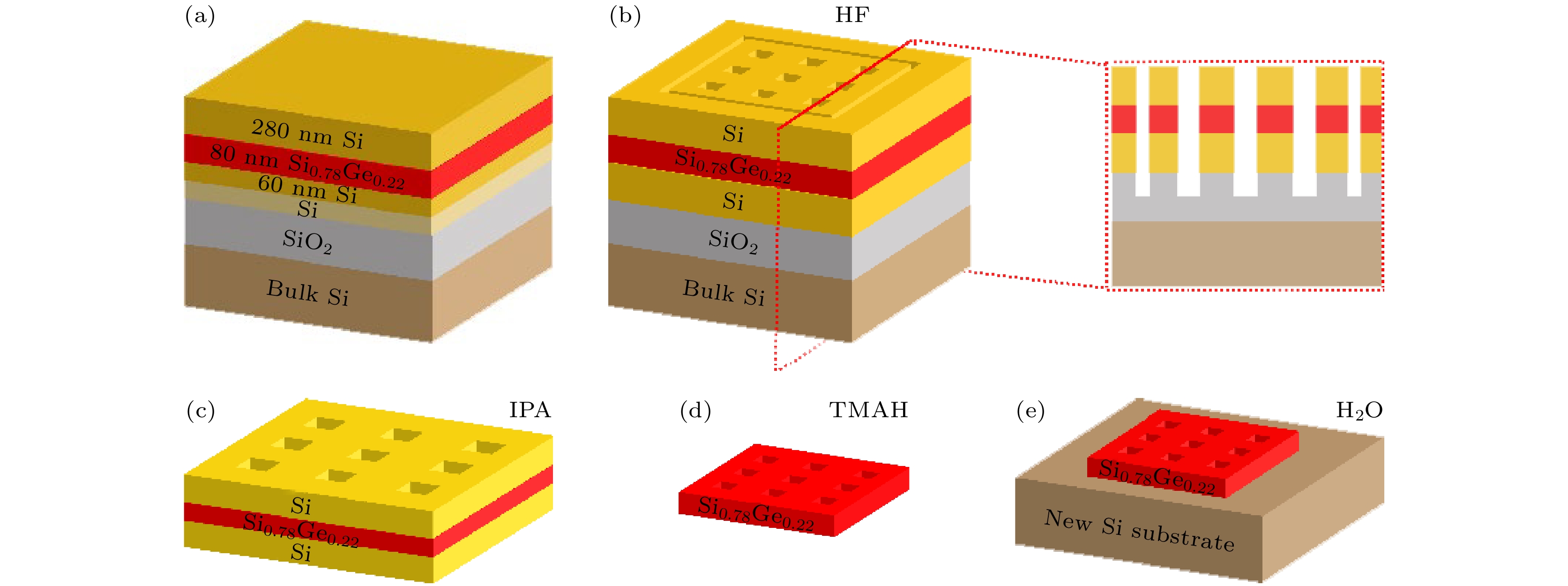

首先是SiGe纳米薄膜的制备, 分为5个步骤. 如图1(a)所示, 第1步, 利用MBE在SOI衬底上生长Si/SiGe/Si异质结结构, 其中SOI衬底上顶层Si厚度为220 nm, Si和Ge的生长速率分别为0.41 Å/s和0.12 Å/s. SOI样品进MBE腔体之前使用稀释的氢氟酸(HF)溶液去除表面自然氧化层并形成氢键钝化的表面, 进腔体后升温至700 ℃进行脱氢, 然后降温至400 ℃, 在此温度下依次外延沉积60 nm Si, 80 nm Si0.78Ge0.22和280 nm Si. SiGe层上下的Si层厚度需保持一致, 均为280 nm, 以避免在后续刻蚀Si层过程中SiGe薄膜的卷曲[25]. 第2步, 如图1(b)所示, 利用激光直写和感应耦合等离子体(ICP)刻蚀出间隔为200 μm的周期孔洞阵列至SiO2层, 进而通过浓度为49%的HF溶液选择性腐蚀掉SiO2层. 第3步, 将衬底和黏附Si/SiGe/Si异质结结构的样品转移到异丙醇(IPA)溶液中进行分离, 制备出如图1(c)所示尺寸为2 mm×2 mm的异质结薄膜. 第4步, 通过10%四甲基氢氧化铵(TMAH)溶液选择性刻蚀异质结薄膜的上下Si层, 获得如图1(d)所示的SiGe纳米薄膜. 第5步, 经过在去离子水中多次清洗后, 在水中将薄膜转移到Si(001)衬底(图1(e)).

在此应力弛豫的Si(001) SiGe纳米薄膜上, 我们二次外延生长了Si/SiGe异质结二维电子气. 在样品进入MBE腔体之前, 如前所述, 样品使用稀释的HF溶液去除表面自然氧化层并形成氢键. 传入MBE腔体后, 在3×10–11 mbar (1 bar = 105 Pa)的高背景真空下, 先后在500 ℃和700 ℃保持15 min进行除气和脱氢. 随后将温度降至400 ℃以Si 0.41 Å/s, Ge 0.12 Å/s的生长速率沉积100 nm Si0.78Ge0.22缓冲层, 然后升温至550 ℃后依次外延200 nm Si0.78Ge0.22缓冲层, 12 nm应变Si层, 35 nm Si0.78Ge0.22间隔层和2 nm Si盖层.

我们对转移SiGe薄膜上的二维电子气异质结进行了详细的表征. 利用快速显微共聚集拉曼成像系统(Horiba/LabRam HR Evolution)在1800 nm光栅、532 nm激光下, 对比分析了转移前和转移后的SiGe纳米薄膜, Si/SiGe异质结的应变状态. 使用原子力显微镜(Bruker/Dimension Icon)在轻敲模式下表征了样品的表面形貌. 使用基于场发射扫描电子显微镜(ZEISS/Gemini 300)的电子通道衬度成像技术, 在15 kV的加速电压下, 对样品表面的穿透位错进行了表征. 利用球差校正透射电镜(JEOL/JEM-ARM300 F2)对样品的界面进行了表征.

-

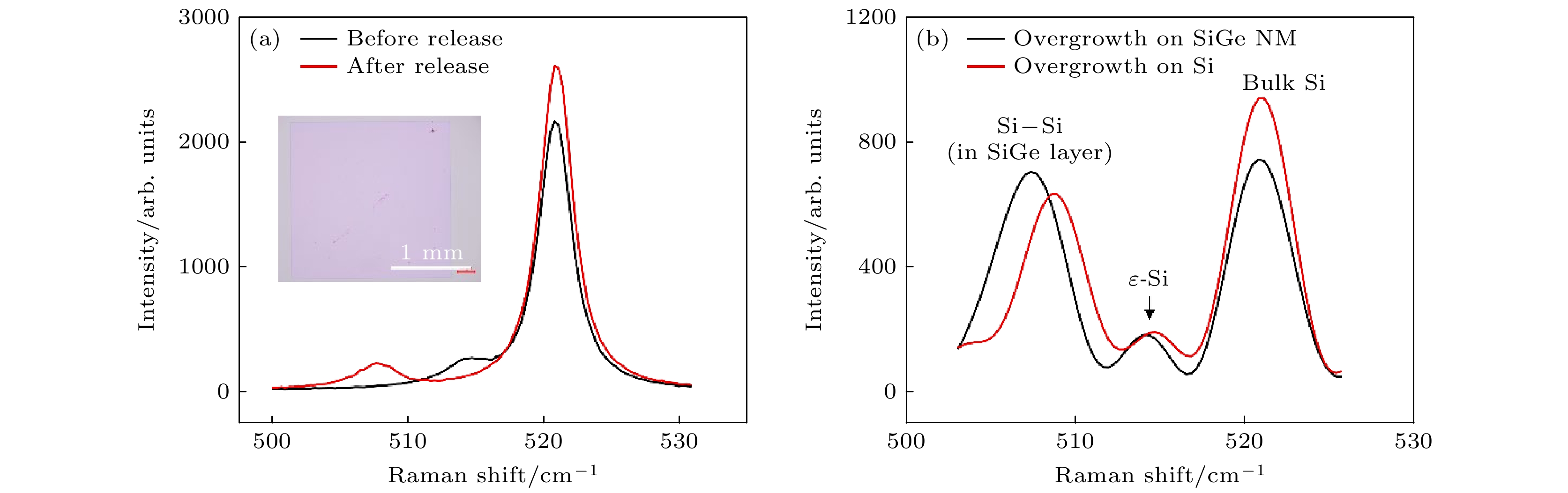

为了研究SiGe纳米薄膜中的应变状态, 如图2(a)所示, 使用拉曼测量了Si(001)衬底上SiGe薄膜释放前后的Si—Si峰的频移. 插图是2 mm × 2 mm SiGe纳米薄膜转移到Si(001)衬底后的光学显微图. 实验基于上下Si层相同厚度的对称性设计, 在刻蚀过程中同步去除上下Si层, 促使应力对称地释放, 有效抑制薄膜卷曲, 最终实现优异的面内均匀性. 在释放和转移SiGe纳米薄膜后, Si—Si峰发生红移, 说明平面内晶格常数增大, 发生了弹性弛豫现象. 对于(001)平面上的双轴应变, SiGe纳米薄膜中Si—Si峰的频率偏移

$ \Delta {\omega _{{\text{Si—Si}}}} $ 和SiGe层中双轴平面应变$ {\varepsilon _{{\text{SiGe}}}} $ 呈线性关系:$ \Delta {\omega_{\text{Si—Si}}} = {b_{{\text{Si—Si}}}}{\varepsilon _{{\text{SiGe}}}} $ [26] , 其中$ {b_{{\text{Si—Si}}}} $ 是基于SiGe弹性常数和声子形变势能的常数, 已经有实验算得$ {b_{{\text{Si—Si}}}} = {\text{ }}( - 730{\text{ }} \pm {\text{ }}70){\text{ c}}\text{m}^{ - 1} $ [27], 该误差范围主要由塑性弛豫SiGe衬底的应变不均匀性及表面起伏引起. 根据文献[27]可计算出, 完全应变状态下Si0.78Ge0.22的双轴平面应变约为0.83%, 其在完全弛豫状态下的偏移范围为5.476—6.640 cm–1. 对于本实验使用的拉曼光谱仪, 分辨率为0.35 cm–1, 实验误差在0.5 cm–1附近. 实验测得释放前后, SiGe纳米薄膜中Si—Si峰的偏移量为(6.402 ± 0.5) cm–1, 测量数值在理论计算的偏移范围之内. 同时我们也通过X射线衍射(XRD)测量确认了薄膜中的Ge约为22%, 说明转移Si0.78Ge0.22薄膜中的应力完全释放. 如图2(b)所示, 实验测量显示在转移的SiGe纳米薄膜上二次外延的Si/SiGe异质结薄膜中Si—Si峰的位置没有发生改变, 说明经历二次外延的升降温和同质、异质外延后, 应力弛豫的SiGe纳米薄膜薄依然保持弛豫的状态. 从图2(b)还可观察到应变Si峰的存在, 实验测得Si/Si0.78Ge0.22异质结量子阱中应变Si峰与衬底Si峰的差值为(6.609 ± 0.5) cm–1. 对于(001)平面上的双轴应变, 如上述, 根据公式$ \Delta {\omega _{{\text{Si}}}} = {b_{{\text{Si}}}}{\varepsilon _{{\text{Si}}}} $ [28], 其中,$ \Delta {\omega _{{\text{Si}}}} $ 是无应变Si层和应变Si层的频移差值,$ {b_{{\text{Si}}}} $ 是对应的应变偏移系数,$ {\varepsilon _{{\text{Si}}}} $ 是Si/Si1–xGex异质结中Si量子阱(Si QW)平面内的应变. 22% Ge含量的Si/Si0.78Ge0.22异质结中Si量子阱平面内的应变εSi = 0.84 %, 根据先前实验计算的bSi = (–784 ± 4) cm–1[29], 实验理论值和拉曼测试结果吻合良好. 在Si衬底区域(非SiGe纳米膜覆盖区域)生长的Si/SiGe异质结, 失配应力由产生位错的形式来释放, 由于SiGe缓冲层中的应力没有得到完全弛豫, 拉曼测得SiGe中Si—Si峰和应变Si峰的频率位置更靠近衬底Si峰, 符合预期. -

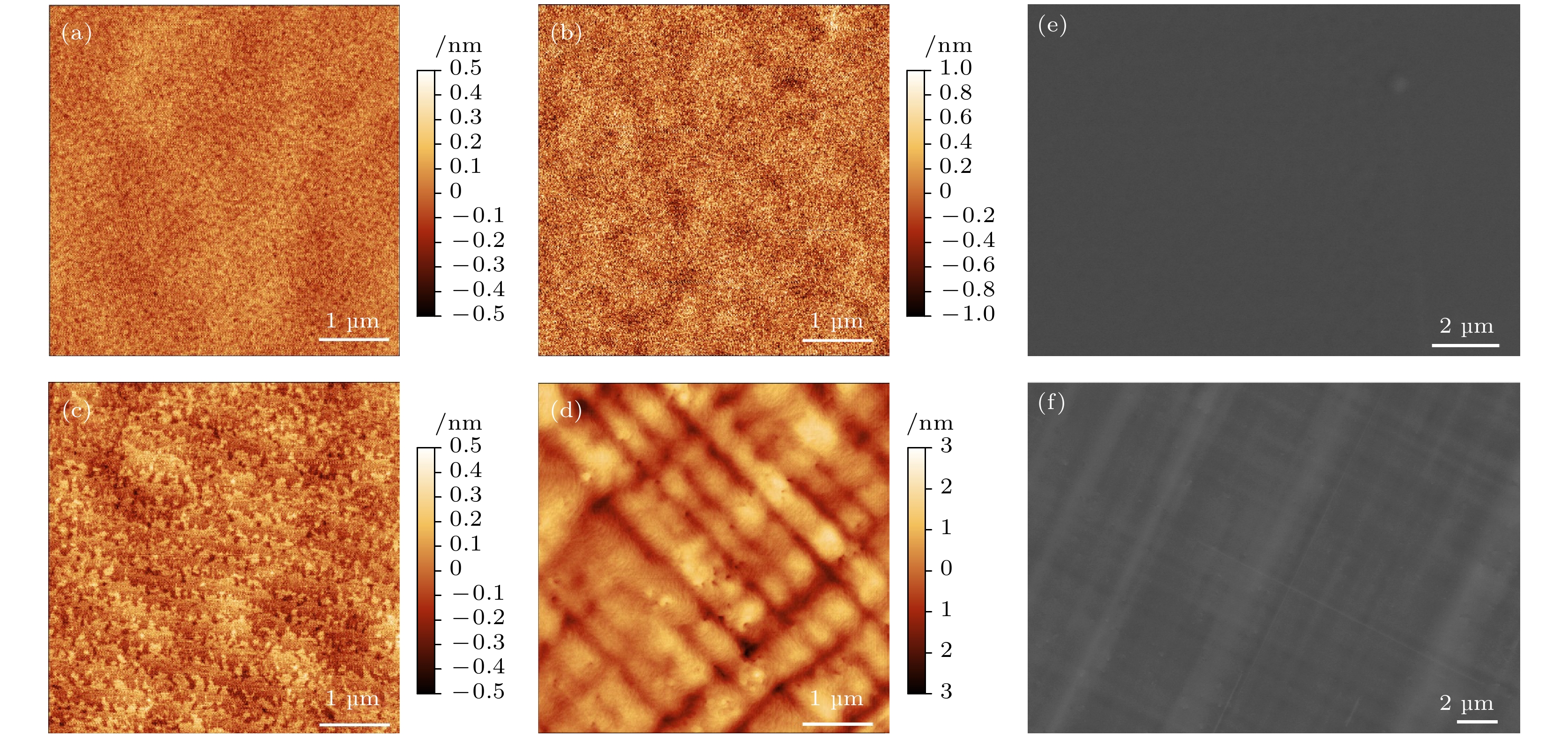

图3(a)展示了SOI衬底上外延Si/SiGe/Si结构后的表面AFM图, 扫描尺寸5 μm × 5 μm. 样品表面平整度达到原子级别, 均方根粗糙度(RMS roughness)约为0.089 nm, 无交叉线现象, 表明外延的SiGe层厚度低于产生三维岛的临界厚度, 且没有产生任何失配位错. 图3(b)显示了应力弛豫的SiGe纳米薄膜转移到Si衬底后的5 μm × 5 μm AFM图. 样品表面均方根粗糙度为0.323 nm, 数值相对转移前结构表面粗糙度略有升高, 原因在于TMAH水溶液腐蚀Si和Si0.78Ge0.22的选择比接近30∶1[30,31], 低选择比使得SiGe表层略微被刻蚀. 但是TMAH刻蚀均匀性较高, SiGe纳米薄膜表面仍保持原子级别的起伏. 图3(c)显示了在转移的SiGe纳米膜上二次外延Si/SiGe异质结后的AFM图像. 样品表面平整度高, 原子尺度上可清晰观察到原子台阶. 5 μm × 5 μm区域表面均方根粗糙度仅为0.118 nm, 表明生长的Si/SiGe异质结具有很高的晶体质量和均匀性. 低表面起伏能有效降低载流子输运过程中的界面粗糙度散射, 提升载流子迁移率, 从而提高器件性能. 图3(d)对比了同一片衬底, 非纳米薄膜区域直接外延生长的Si/SiGe异质结样品表面, 5 μm × 5 μm区域表面均方根粗糙度为0.661 nm, 远高于SiGe纳米薄膜区域. 生长的300 nm Si0.78Ge0.22超出了临界厚度, 发生了塑形应变弛豫. 从图3(d)观察到明显的交叉线现象和大量的坑洞, 即穿透位错在表面的露头. 计算其中坑的数量, 可得穿透位错密度大致为1.56×108 cm–2. 非纳米薄膜区域直接外延生长的Si/SiGe异质结存在高表面起伏和位错, 给载流子输运带来额外的散射因素, 会极大地影响器件的电学性能. 图3(e), (f)对比了转移SiGe纳米薄膜区域和Si衬底区域生长Si/SiGe异质结后的ECCI图像. 转移SiGe纳米薄膜区域未观察到任何穿透位错, 且呈现出均匀的衬度对比. 从图3(f)可以看到交叉线结构, 这是因为Si衬底上直接生长SiGe薄膜, 内部产生大量失配位错并滑移, 因此造成薄膜应变分布不均匀. 其中穿透位错密度约为9.3×107 cm–2. 穿透位错的存在造成了SiGe薄膜层和应变硅量子阱层的应力弛豫, 解释了拉曼数据中的峰位偏移现象. 特别说明的是, 图3(e)中右上角的脏点是为了聚焦特地选取的区域.

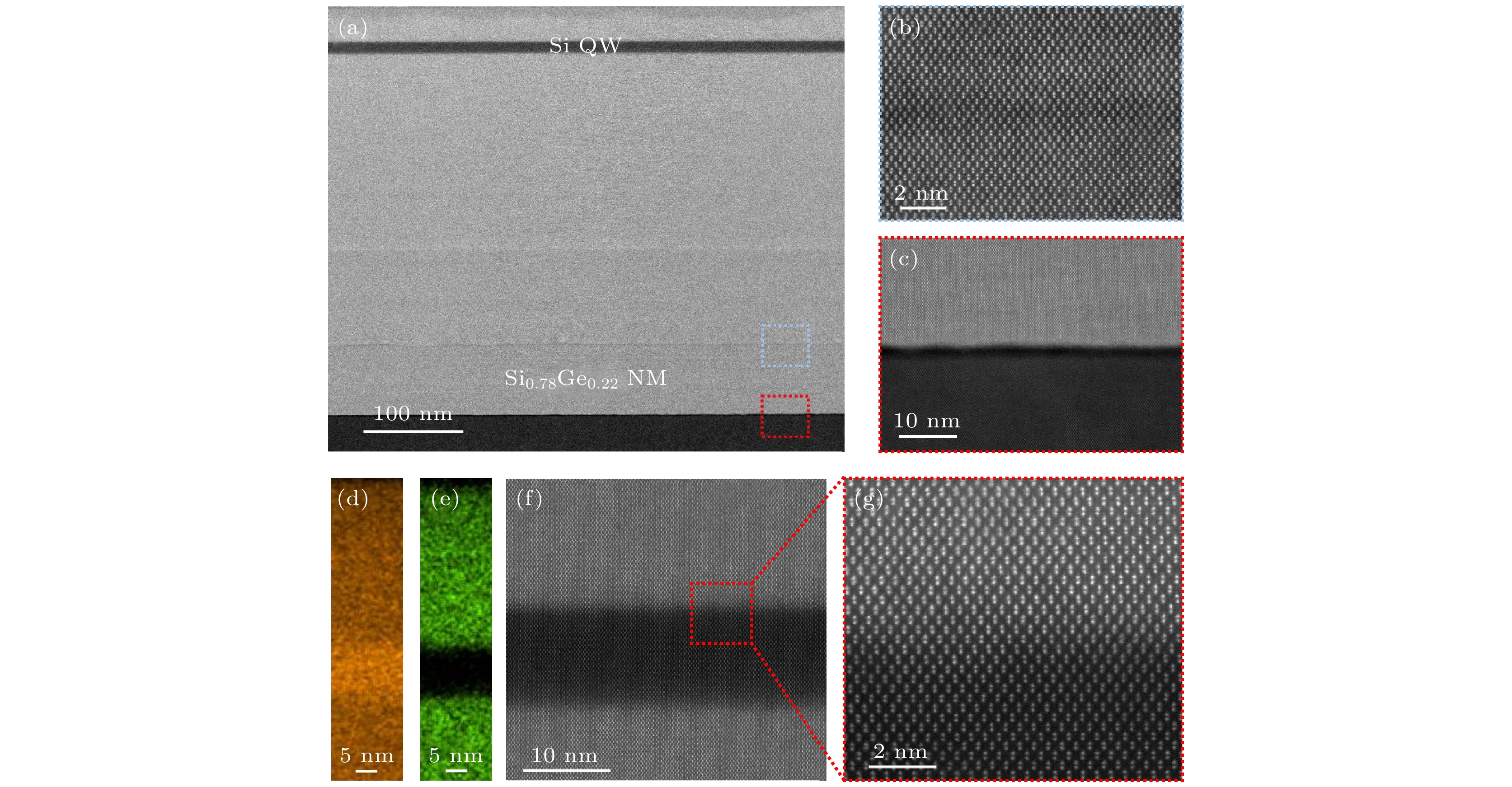

进一步, 我们详细研究了异质结的界面, 在STEM-HAADF模式下, 如图4(a)所示, 底部区域可以清晰地观察到转移SiGe纳米薄膜与Si衬底, 以及转移SiGe薄膜与外延薄膜的界面. 转移的SiGe纳米薄膜没有观察到硅层的残留, 表明SiGe薄膜的应力可以在刻蚀溶液中自由弛豫, 佐证了拉曼数据的表征结果. 此外, 转移的SiGe纳米薄膜中没有观察到任何的位错, MBE二次外延异质结中也没有观测到位错. 图4(b)是SiGe纳米薄膜和外延薄膜界面的原子分辨高倍率放大图, 显示完美的晶格匹配. 图4(c)是Si衬底和转移SiGe纳米薄膜界面的高倍率放大图. 界面处可以观察到Si衬底表面自然氧化的约2 nm SiO2层, 但该氧化层的存在并没有影响后续的异质结外延. 图4(d), (e)分别为Si量子阱附近的Si元素和Ge元素的能量色散X射线谱. 图中明暗程度代表了对应元素分布的情况, 可以清晰地看到Si量子阱和SiGe层之间的清晰界面. 图4(f)是转移SiGe衬底上Si/SiGe界面STEM-HAADF图像, 图4(g)是界面处的原子分辨高倍率放大图, 图中未观察到任何缺陷. 系列表征都确认了在转移SiGe纳米薄膜上生长的Si/SiGe异质结是无缺陷的单晶.

-

本工作通过在SOI衬底上外延Si/SiGe/Si异质结, 利用湿法刻蚀SO2和上下Si层来剥离异质结和释放SiGe层中的应力, 制备出了2 mm × 2 mm的无位错缺陷、高平整度、应力弛豫的单晶SiGe纳米薄膜, 然后将此薄膜转移至Si(001)衬底上并进行Si/SiGe异质结的二次外延, 成功实现了表面粗糙度仅为0.118 nm、没有位错缺陷的大面积Si/SiGe二维异质结. 研究工作为实现高迁移率二维电子气和高性能量子比特奠定了重要的材料基础.

基于转移SiGe薄膜上的高质量Si/SiGe异质结

High-quality Si/SiGe heterojunctions on transferred SiGe nanomembranes

-

摘要: 高质量的Si/SiGe异质结薄膜材料在集成电路和半导体量子计算等领域都有重要的应用. 本研究首先通过分子束外延(MBE)在SOI衬底上获得上下Si层厚度一致的Si/SiGe/Si异质结; 随后利用湿法刻蚀剥离该异质结, 并接着刻蚀上下Si层, 得到应力弛豫的SiGe薄膜; 最后, 将其转移到Si(001)衬底上并再次使用MBE在该转移SiGe薄膜上外延制备SiGe/Si/SiGe异质结. 原子力显微镜表征显示异质结表面均方根粗糙度仅为0.118 nm, 透射电子显微镜和电子通道衬度成像均未观察到任何位错. 研究显示基于转移SiGe薄膜上的Si/SiGe异质结完全消除了晶格失配引起的位错缺陷, 为高性能的量子比特器件奠定了重要的材料基础.Abstract: Strained silicon technology employing strain-relaxed SiGe virtual substrates has become pivotal factor in advancing group IV semiconductor electronics, photonic devices, silicon-based quantum computing architectures, and neuromorphic devices. Although existing approaches using Si/SiGe superlattice buffers and compositionally graded SiGe layers can produce high-quality SiGe virtual substrates, defects including threading dislocations and crosshatch patterns still limit further performance enhancement. This study demonstrates a method of fabricating fully elastically relaxed SiGe nanomembranes that effectively suppresses the formation of both threading dislocations and crosshatch patterns. The fabrication process comprises three key steps: 1) epitaxially growing Si/SiGe/Si heterostructures on silicon-on-insulator substrates via molecular beam epitaxy (MBE), 2) fabricating periodic pore arrays by using photolithography and reactive ion etching, and 3) selectively wet etching and subsequently transferring nanomembranes to Si(001) substrates. Subsequently, a Si/SiGe heterostructure is grown on the SiGe nanomembranes via MBE. The full elastic relaxation state of the SiGe nanomembranes and the fully strained state of the Si quantum well in the epitaxial Si/SiGe heterostructures are verified using Raman spectroscopy. Surface root-mean-square roughness value is 0.323 nm for the SiGe nanomembrane transferred to the silicon substrate and 0.118 nm for the epitaxial Si/SiGe heterostructure, which are demonstrated through atomic force microscopy measurements. Through electron channel contrast imaging, it is demonstrated that the Si/SiGe heterostructures grown on SiGe nanomembranes have uniform surface contrast and no detectable threading dislocations. Comparatively, the silicon substrate region exhibits high-density threading dislocations accompanied by stacking faults. Cross-sectional transmission electron microscope analysis shows atomically sharp and defect-free interfaces. This research lays a critical foundation for developing high-mobility two-dimensional electron gas systems and high-performance quantum bits.

-

Key words:

- molecular beam epitaxy /

- stress relaxation /

- SiGe /

- heterojunction .

-

-

图 1 SiGe纳米薄膜的制备流程 (a) SOI衬底上外延生长60 nm Si, 80 nm Si0.78Ge0.22和280 nm Si; (b) 利用微纳加工技术制备周期孔洞阵列; (c) 在IPA溶液中将Si/SiGe/Si异质结和衬底进行分离; (d) 在TMAH溶液中选择性刻蚀掉上下Si层后的SiGe薄膜; (e) 在去离子水中将SiGe纳米薄膜转移到Si(001)衬底上

Figure 1. Fabrication processes of SiGe nanomembrane: (a) MBE epitaxial growth of 60 nm Si, 80 nm Si0.78Ge0.22, and 280 nm Si on an SOI substrate; (b) fabrication of a periodic hole array on such heterostructure; (c) separation of the Si/SiGe/Si heterostructure from the Si substrate in IPA solution; (d) selective etching of the Si layers over SiGe in TMAH solution; (e) transfer of the SiGe nanomembrane onto a Si (001) substrate in deionized water.

图 2 (a) Si0.78Ge0.22纳米薄膜在释放前(黑线)和释放后(红线)的拉曼光谱, 其中插图是Si0.78Ge0.22纳米膜转移到Si衬底后的光学显微镜图; (b) 在Si0.78Ge0.22纳米薄膜区域(黑线)和Si衬底区域(红线)生长Si/SiGe异质结后的拉曼光谱

Figure 2. (a) Raman spectra of Si0.78Ge0.22 nanomembrane before release (black line) and after release (red line), where the inset shows an optical microscope image of the Si0.78Ge0.22 nanomembrane transferred to a Si substrate; (b) Raman spectra after growing Si/SiGe heterostructure in the Si0.78Ge0.22 nanomembrane region (black line) and Si substrate region (red line).

图 3 (a) SOI衬底上生长Si/SiGe/Si异质结后的表面AFM图; (b) Si0.78Ge0.22纳米薄膜转移到Si衬底后的表面AFM; (c) 转移Si0.78Ge0.22纳米薄膜区域上生长Si/SiGe异质结后的表面AFM图; (d) 在Si衬底区域直接生长Si/SiGe异质结后的表面AFM图; (e) 在Si0.78Ge0.22纳米薄膜区域生长Si/SiGe异质结后的表面ECCI图; (f)在Si衬底区域直接生长Si/SiGe异质结后的表面ECCI图

Figure 3. (a) AFM image of the surface after growing Si/SiGe/Si structure on an SOI substrate; (b) AFM image of the surface after transferring Si0.78Ge0.22 nanomembrane to a Si substrate; (c) AFM image of the surface after growing Si/SiGe heterostructure on the transferred Si0.78Ge0.22 nanomembrane region; (d) AFM image of the surface after directly growing Si/SiGe heterostructure on the Si region; (e) electron channel contrast imaging (ECCI) of the surface after growing Si/SiGe heterostructure on the Si0.78Ge0.22 nanomembrane region; (f) ECCI of the surface after directly growing Si/SiGe heterostructure on the Si substrate region.

图 4 (a) Si(001)衬底上转移Si0.78Ge0.22纳米薄膜上生长Si/SiGe异质结后的截面STEM-HAADF原子图像; (b) 转移Si0.78Ge0.22纳米薄膜与外延Si0.78Ge0.22薄膜的截面STEM-HAADF原子图像; (c) Si衬底与Si0.78Ge0.22纳米薄膜界面的高倍STEM-HAADF原子图像; (d) Si量子阱附近的Si元素EDS谱; (e) Si量子阱附近的Ge元素EDS谱; (f) Si量子阱附近的高倍STEM-HAADF原子图像; (g) Si量子阱与Si0.78Ge0.22界面处的STEM-HAADF原子图像

Figure 4. (a) STEM-HAADF image after growing Si/SiGe heterostructure on transferred Si0.78Ge0.22 nanomembrane on Si (001); (b) STEM-HAADF image showing the interface between the transferred and epitaxial Si0.78Ge0.22; (c) high-magnified STEM-HAADF image showing the interface between the Si substrate and transferred Si0.78Ge0.22 nanomembrane; (d) EDS spectrum of Si element near the Si quantum well; (e) EDS spectrum of Ge element near the Si quantum well; (f) high-magnified STEM-HAADF image near the Si quantum well; (g) STEM-HAADF atomic image showing the interface between the Si quantum well and the Si0.78Ge0.22 spacer layer.

-

[1] Theis T N, Wong H S P 2017 Comput. Sci. Eng. 19 41 doi: 10.1109/MCSE.2017.29 [2] Shalf J 2020 Philos. Trans. R. Soc. Math. Phys. Eng. Sci. 378 20190061 doi: 10.1098/rsta.2019.0061 [3] Thompson S E, Parthasarathy S 2006 Mater. Today 9 20 doi: 10.1016/S1369-7021(06)71539-5 [4] Arienzo M, Iyer S S, Meyerson B S, Patton G L, Stork J M C 1991 Appl. Surf. Sci. 48 377 doi: 10.1016/0169-4332(91)90361-M [5] Azevedo A M D, Lopes T J, Cardoso D D, Monterio S N, Silveira P C R, Figueiredo A B H D S 2024 Obs. Econ. Latinoam. 22 e8370 doi: 10.55905/oelv22n12-219 [6] Cressler J D 1998 IEEE Trans. Microw. Theory Tech. 46 572 doi: 10.1109/22.668665 [7] Harame D L, Koester S J, Freeman G, Cottrel P, Rim K, Dehlinger G, Ahlgren D, Dunn J S, Greenberg D, Joseph A, Anderson F, Rieh J S, Onge S A S T, Coolbaugh D, Ramachandran V, Cressler J D, Subbanna S 2004 Appl. Surf. Sci. 224 9 doi: 10.1016/j.apsusc.2003.08.086 [8] Soref R A 1993 Proc. IEEE 81 1687 doi: 10.1109/5.248958 [9] Wang K L, Cha D, Liu J, Chen C 2007 Proc. IEEE 95 1866 doi: 10.1109/JPROC.2007.900971 [10] 张结印, 高飞, 张建军 2021 物理学报 70 217802 doi: 10.7498/aps.70.20211492 Zhang J Y, Gao F, Zhang J J 2021 Acta Phys. Sin. 70 217802 doi: 10.7498/aps.70.20211492 [11] Tai C T, Li J Y 2024 Mater. Quantum Technol. 4 012001 doi: 10.1088/2633-4356/ad2980 [12] Connors E J, Nelson J, Edge L F, Nichol J M 2022 Nat. Commun. 13 940 doi: 10.1038/s41467-022-28519-x [13] Bian H, Goh Y Y, Liu Y, Ling H, Xie L, Liu X 2021 Adv. Mater. 33 2006469 doi: 10.1002/adma.202006469 [14] Fitzgerald E A, Xie Y H, Green M L, Brasen D, Kortan A R, Michel J, Mii Y J, Weir B E 1991 Appl. Phys. Lett. 59 811 doi: 10.1063/1.105351 [15] Hartmann J M, Gallas B, Zhang J, Harris J J, Joyce B A 1999 J. Appl. Phys. 86 845 doi: 10.1063/1.370813 [16] Rahman M M, Matada H, Tambo T, Tatsuyama C 2001 Appl. Surf. Sci. 175 6 doi: 10.1016/S0169-4332(01)00049-6 [17] Nelson S F, Ismail K, Nocera J J, Fang F F, Mendez E E, Chu J O, Meyerson B S 1992 Appl. Phys. Lett. 61 64 doi: 10.1063/1.107670 [18] 耿鑫, 张结印, 卢文龙, 明铭, 刘方泽, 符彬啸, 褚逸昕, 颜谋回, 王保传, 张新定, 郭国平, 张建军 2024 物理学报 73 117302 doi: 10.7498/aps.73.20240310 Geng X, Zhang J Y, Lu W L, Ming M, Liu F Z, Fu B X, Chu Y X, Yan M H, Wang B C, Zhang X D, Guo G P, Zhang J J 2024 Acta Phys. Sin. 73 117302 doi: 10.7498/aps.73.20240310 [19] Xie Y H, Fitzgerald E A, Mii Y J, Monroe D, Thiel F A, Weir B E, Feldman L C 1991 MRS Proc. 220 413 doi: 10.1557/PROC-220-413 [20] Ismail K 1996 J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 14 2776 doi: 10.1116/1.588831 [21] Monroe D, Xie Y H, Fitzgerald E A, Silverman P J, Watson G P 1993 J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 11 1731 doi: 10.1116/1.586471 [22] Paskiewicz D M, Tanto B, Savage D E, Lagally M G 2011 ACS Nano 5 5814 doi: 10.1021/nn201547k [23] Li Y S, Sookchoo P, Cui X, Mohr R, Savage D E, Foote R H, Jacobson R, Sánchez-Pérez J R, Paskiewicz D M, Wu X, Ward D R, Coppersmith S N, Eriksson M A, Lagally M G 2015 ACS Nano 9 4891 doi: 10.1021/nn506475z [24] Schäffler F 1997 Semicond. Sci. Technol. 12 1515 doi: 10.1088/0268-1242/12/12/001 [25] Schmidt O G, Eberl K 2001 Nature 410 168 doi: 10.1038/35065525 [26] Wolf I D 1996 Semicond. Sci. Technol. 11 139 doi: 10.1088/0268-1242/11/2/001 [27] Pezzoli F, Bonera E, Grilli E, Guzzi M, Sanguinetti S, Chrastina D, Isella G, Von Känel H, Wintersberger E, Stangl J, Bauer G 2008 J. Appl. Phys. 103 093521 doi: 10.1063/1.2913052 [28] Nakashima S, Mitani T, Ninomiya M, Matsumoto K 2006 J. Appl. Phys. 99 053512 doi: 10.1063/1.2178396 [29] Wong L H, Wong C C, Liu J P, Sohn D K, Chan L, Hsia L C, Zang H, Ni Z H, Shen Z X 2005 Jpn. J. Appl. Phys. 44 7922 doi: 10.1143/JJAP.44.7922 [30] Loup V, Gabette L, Roure M C, Kachtouli R, Jourdan M, Besson P, Petitdidier S 2013 ECS Trans. 58 47 doi: 10.1149/05806.0047ecst [31] Shikida M, Sato K, Tokoro K, Uchikawa D 2000 Sens. Actuators Phys. 80 179 doi: 10.1016/S0924-4247(99)00264-2 -

首页

首页 登录

登录 注册

注册

下载:

下载: