-

二维半导体材料凭借其本征原子级平整的表面结构与可调节的电子能带结构等独特优势, 为构建高性能场效应晶体管(field-effect transistor, FET)提供了理想平台[1–4], 在后摩尔时代高密度集成电路领域展现出巨大应用潜力[5–12]. 现代集成电路中低功耗与高稳定性的双重特性, 本质上由p型FET(p-FET)与n型FET(n-FET)构成的互补型电路架构所决定. 传统硅基技术中广泛采用离子注入[13]与离子扩散[14]等技术来实现沟道载流子的极性调控, 然而此类基于高能轰击的掺杂手段并不适用于二维材料体系. 二维材料的原子级薄层结构对晶格完整性极度敏感, 高能离子辐照诱导的缺陷态不仅显著劣化载流子输运性能, 同时增加材料中的缺陷密度, 进而诱导二维材料和源漏电极接触界面的费米钉扎效应, 限制载流子注入类型和效率的有效调控. 为突破此限制, 领域内相继发展了一系列极性调控策略, 包括: 通过表面吸附诱导的电荷转移掺杂技术[15–20], 利用范德瓦耳斯接触实现金属功函数匹配的半导体载流子注入类型调控技术[21,22], 栅极电场对沟道载流子浓度与类型的静电调控技术[23–25], 以及利用界面电荷转移诱导的半导体极性重构技术[26]等. 当前发展的极性调控方法为二维半导体器件性能优化提供了可行方案, 但其在制造工艺的简易性和可控性方面仍与成熟的硅基技术存在明显差距, 这已成为二维互补逻辑电路规模化应用的主要制约因素.

本研究发展了一种基于一步热退火工艺的简便有效的二维半导体极性调控新策略. 具有不同金属电极接触的WSe2 FETs退火前后的电学特性表征结果表明, Pd电极接触的WSe2 FETs经退火后的导电特性由n型主导转变为p型主导; 而Cr电极接触的器件则始终保持n型主导的导电特性. 基于该极性调控策略, 我们通过在同一WSe2上选择性制备不同金属材料的源漏电极, 结合一步退火工艺实现了互补晶体管(p-FET/n-FET)的单片集成, 并构建互补逻辑反相器电路. 反相器在2.5 V电源电压下展现出优异性能, 其电压增益达23, 总噪声容限达2.3 V(0.92 Vdd). 本研究不仅为二维半导体的极性调控提供了新方法, 同时为二维互补逻辑电路的设计与集成提供了新思路.

-

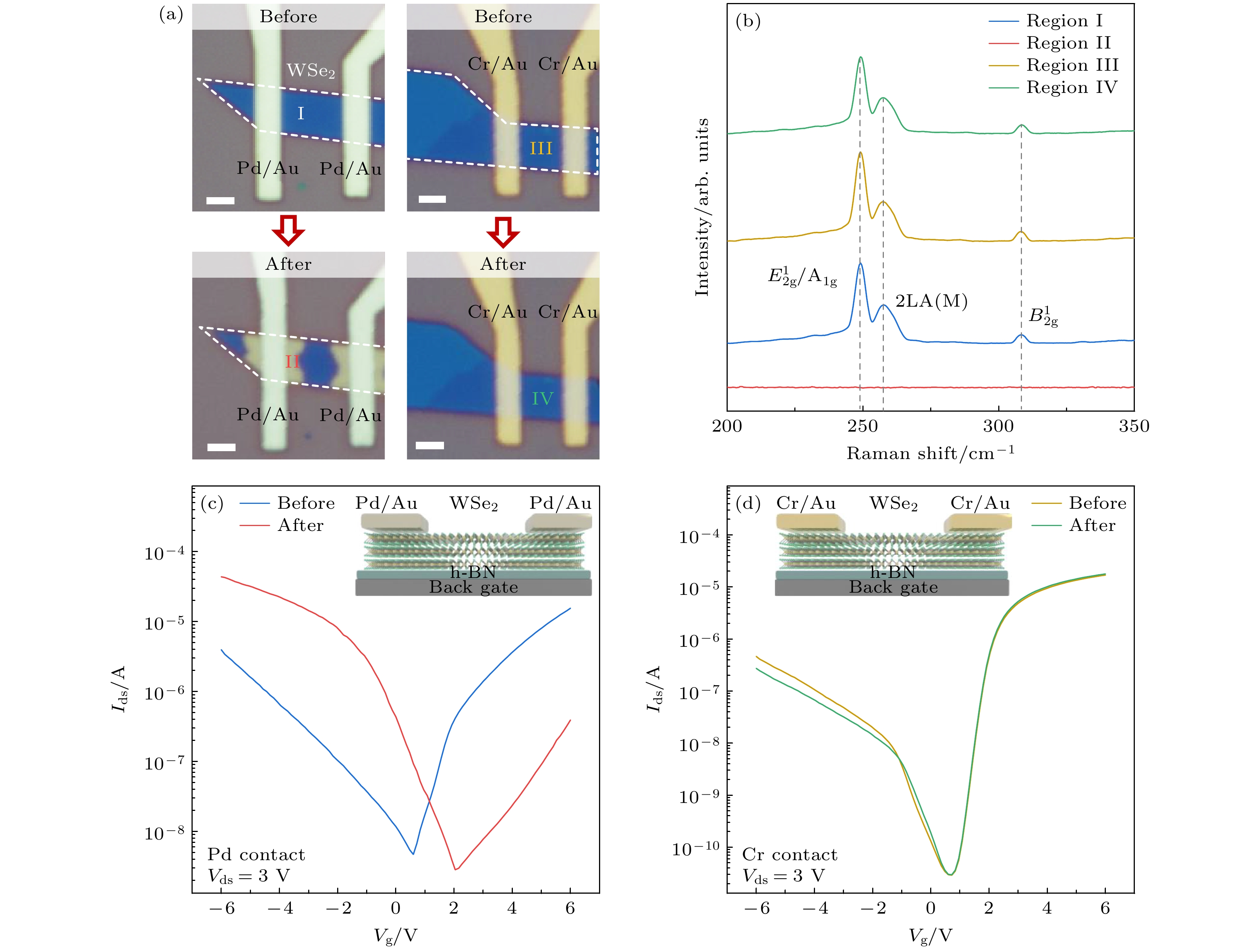

WSe2作为本征双极性半导体, 其场效应特性可通过外场调控实现电子与空穴导电态的动态切换, 为基于单一材料平台的互补逻辑器件的构建提供了物理基础[19,20,23,25,27–29]. 本研究首先探究了WSe2 FETs器件中由热退火诱导的接触界面重构伴随的场效应极性调控行为. 采用机械剥离的WSe2作为沟道材料, 利用电子束曝光和电子束蒸镀等微纳加工技术分别制备了以Pd和Cr作为接触电极的FETs器件. 图1(a)展示了器件在热退火处理(200 ℃, Ar气氛下30 min)前后的光学照片, 将Pd-WSe2 (Pd金属作为源漏接触电极)和Cr-WSe2 (Cr金属作为源漏接触电极)器件在退火前后的电极近邻沟道区域分别标记为区域Ⅰ, Ⅱ, Ⅲ和Ⅳ. Pd-WSe2器件中区域Ⅱ(退火后)相较于区域Ⅰ(退火前)发生了明显的光学衬度变化, 表明退火后Pd电极与WSe2沟道间形成了新的界面接触层, 即退火诱导了器件中Pd电极与WSe2沟道界面的重构. 图1(b)所示的拉曼光谱表征结果进一步验证了这一变化: 区域Ⅰ处的拉曼光谱中观察到位于249 cm–1, 257 cm–1, 309 cm–1的特征峰, 分别对应于WSe2的

$ {E}_{\rm 2g}^{1}/A_{\rm 1g} $ , 2LA(M),$ {{B}}_{\rm 2g}^{1} $ 振动模式, 这与已有文献报道结果一致[30–32], 而区域Ⅱ处消失的WSe2特征峰证实了该区域结构的改变. 这一现象与本研究团队先前报道的结果相符[33], 即通过精确控制热退火条件, 可引发由活性金属Pd原子扩散诱导的金属-半导体接触界面重构. 与之相比, 在相同的退火条件下, Cr-WSe2器件中的区域Ⅳ(退火后)和区域Ⅲ(退火前)在光学衬度与拉曼光谱的对比中均未观察到明显变化, 即退火过程中Cr电极和WSe2沟道的界面结构保持不变.随后, 我们探究了具有不同金属材料作为源漏电极的WSe2 FETs器件(以h-BN为栅介质)在退火前后的电学特性变化. Pd-WSe2 FET退火前后的转移特性曲线如图1(c)所示, 测试中所施加的源漏电压(Vds)为3 V. 退火前, 电子导通电流高于空穴导通电流, 器件表现为n型主导的导电特性; 而退火后, 器件转变为p型主导的导电特性, 其中空穴电流相比退火前提升10倍, 而电子电流则降低2个数量级. 此外, 我们通过场效应迁移率(

$ {\mu }_{\mathrm{F}\mathrm{E}} $ )的改变对载流子输运效率的变化进行了定量分析. 迁移率计算表达式为$ {\mu }_{\mathrm{F}\mathrm{E}}=\dfrac{{L}_{\mathrm{c}\mathrm{h}}}{W\times {C}_{\mathrm{g}}{\times V}_{\mathrm{d}\mathrm{s}}}\times \dfrac{\mathrm{d}{I}_{\mathrm{d}\mathrm{s}}}{\mathrm{d}{V}_{\mathrm{g}}} $ , 其中Cg为介电层的单位电容, W和Lch分别为FET的沟道宽度和长度, Ids为源漏电流, Vg为栅极电压. 经退火, 器件的空穴迁移率从5.3 cm2⋅V–1⋅s–1(退火前)提升至13.4 cm2⋅V–1⋅s–1 (退火后); 而电子 迁移率则从8.9 cm2⋅V–1⋅s–1 (退火前)降低至0.45 cm2⋅V–1⋅s–1 (退火后). 退火前后, 器件中电子的输运能力被抑制, 而空穴的输运能力则得到大幅提升, 显著的极性转变归因于热退火诱导的界面重 构[33]. 不同于Pd-WSe2 FET中观察到的极性转变行为, 图1(d)所示的Cr-WSe2 FET经相同条件的退火处理后的转移特性曲线与退火前几乎重叠, 电子导通电流始终高于空穴导通电流, 即退火前后Cr-WSe2 FET器件可保持稳定的n型主导的导电特性. 上述结果表明, 通过在器件源漏区域选择性制备不同金属材料作为接触电极并结合热退火工艺处理, 可实现对WSe2 FETs极性的选择性调控. -

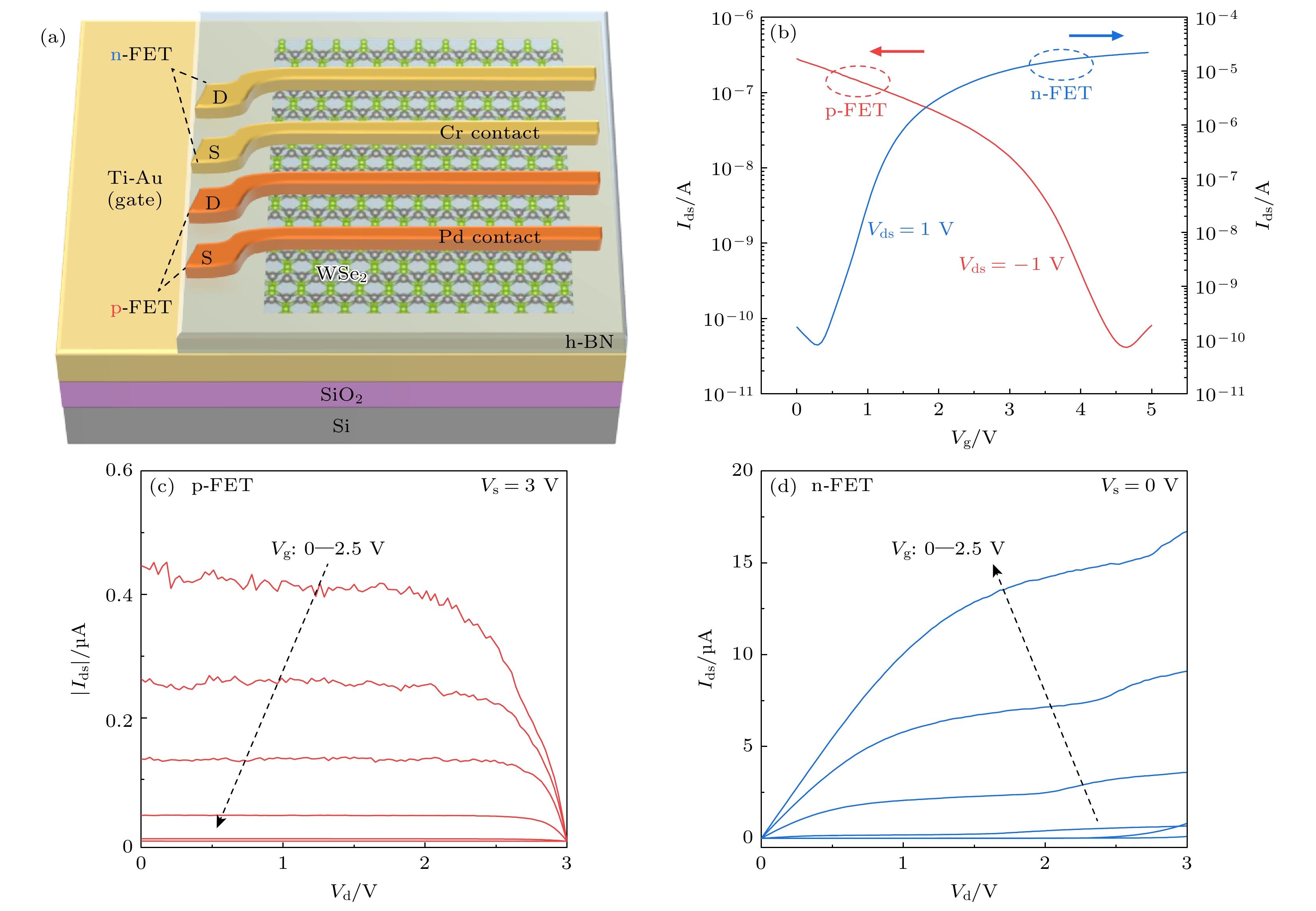

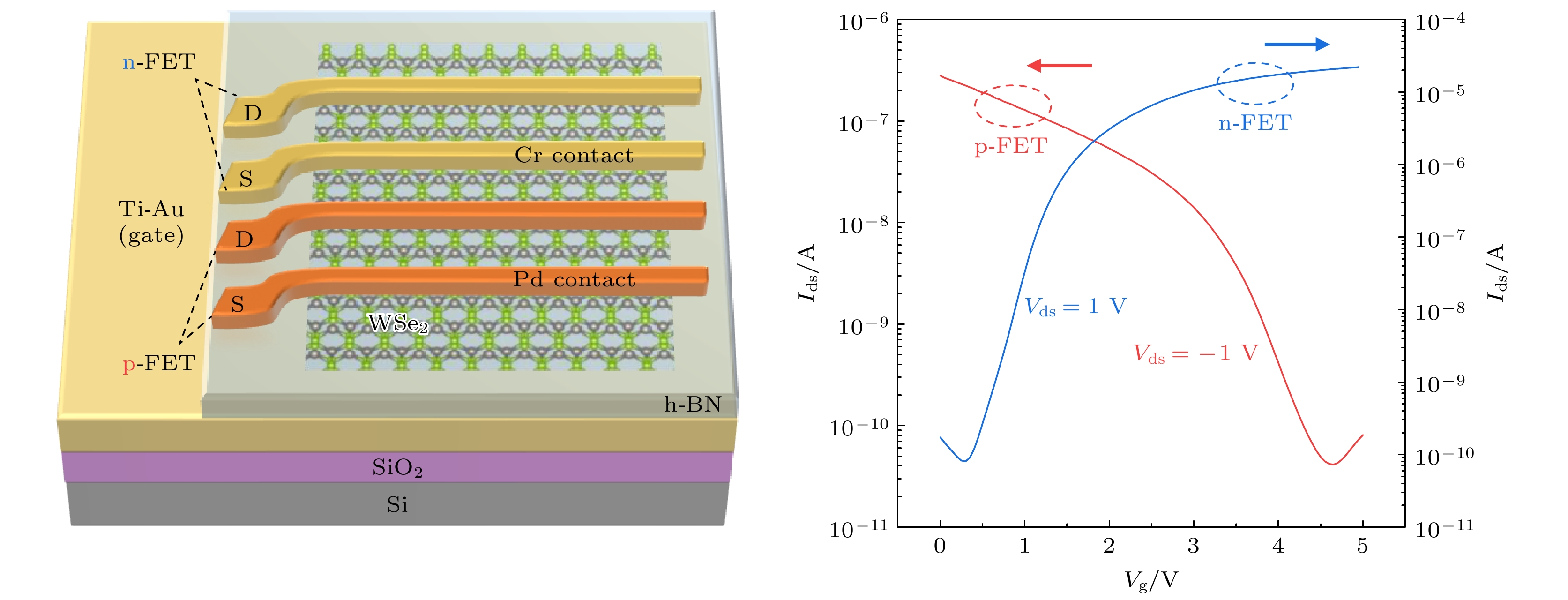

基于上述FETs极性调控策略, 本研究在单一WSe2材料上实现了互补FETs的单片集成. 所构筑的器件中采用机械剥离的WSe2作为沟道材料, h-BN作为栅介质, 并在同一WSe2沟道上制备Pd, Cr两种不同的金属作为源漏电极, 器件结构如图2(a)所示. 经一步退火处理, 形成了具有互补特性的p-FET(Pd-WSe2 FET)和n-FET(Cr-WSe2 FET). 为了验证互补FETs在逻辑电路中的工作性能, 在统一的电压范围内对p-FET与n-FET转移特性和输出特性进行了表征. 器件的转移特性曲线如图2(b)所示, 在0—5 V的Vg范围内, Cr-WSe2 FET在源极接地、漏极施加1 V电压 (Vds = 1 V)的条件下表现出n型场效应特性(蓝色曲线); 而Pd-WSe2 FET在源极施加5 V电压、漏极施加4 V电压(Vds = –1 V)的条件下表现出p型场效应特性(红色曲线). p-FET和n-FET的电流开关比分别超过103和105, 关态电流均小于10–10 A, 开态电流均大于10–7 A, 能够确保互补逻辑电路实现稳定的逻辑状态分离. p-FET和n-FET的输出特性曲线分别如图2(c)与图2(d)所示, 在相同的Vg (0—2.5 V)与Vd (0—3 V)范围内, 在p-FET源极施加3 V偏置电压, 在n-FET源极接地的电学操作下, 两器件均展现出典型的输出电流饱和特性, 这一特性是互补FETs实现高增益反相器电路性能的关键[23]. 综上所述, 基于一步退火法构筑的WSe2互补FETs所展现的优异电学特性为后续研究中逻辑反相器的构建奠定了重要基础.

-

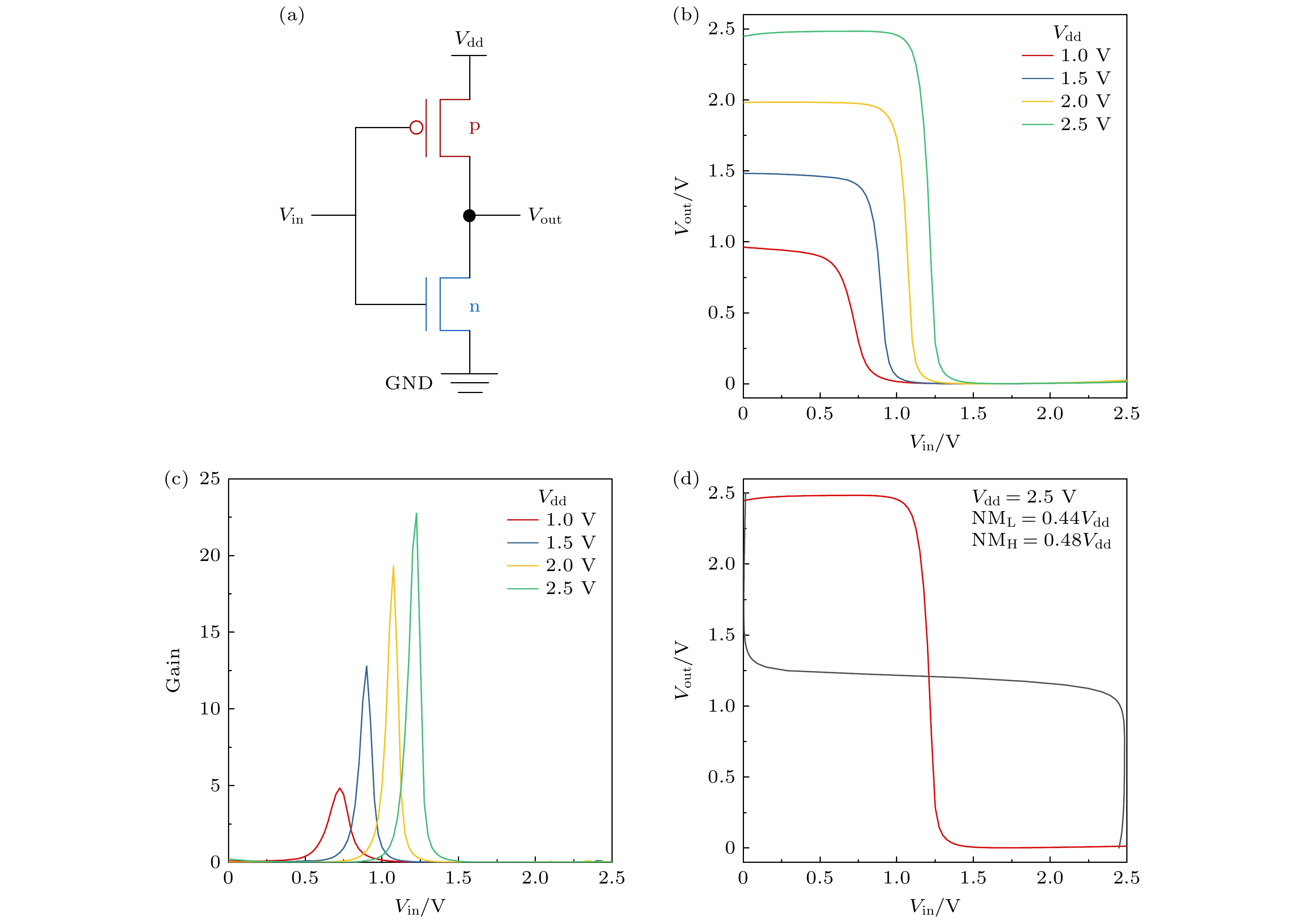

在实现WSe2互补FETs单片集成的基础上, 本研究构建了由p-FET和n-FET串联组成的互补逻辑反相器, 并对其电学性能进行了表征分析. 反相器的电路结构如图3(a)所示, n-FET源极接地(GND), p-FET源极接电源电压(Vdd), 栅极互联形成输入节点(Vin), 漏极互连构成输出节点(Vout). 不同Vdd条件(1.0, 1.5, 2.0, 2.5 V)下反相器的电压传输特性曲线如图3(b)所示, 输出电压摆幅(定义为Vout的最大差值)接近所施加的Vdd, 且输出电压在低输入电压时输出高电平, 在高输入电压时输出低电平, 能够实现稳定的逻辑反转功能. 随后, 基于电压传输特性曲线, 我们进一步量化分析了反相器的两个关键性能指标, 电压增益和噪声容限(noise margin, NM)[27,34], 其中NM包括高噪声容限(NMH)和低噪声容限(NML). 反相器的电压增益如图3(c)所示, 随着Vdd增大, 反相器的增益逐渐增大, 当Vdd = 2.5 V时, 峰值增益达23. 此时, 反相器的NMH与NML分别达到1.2 V(0.48 Vdd)与1.1 V(0.44 Vdd), 总噪声容限(NMtotal = NMH + NML)达2.3 V(0.92 Vdd), 如图3(d)所示. 上述测试结果表明, 本研究所构建的互补逻辑反相器具备良好的信号传输能力和抗干扰能力, 其增益和噪声容限水平与领域内部分代表性研究报道的二维反相器性能相当[15,19,35], 能 够有效地避免因噪声或电压波动引起的逻辑错误, 展现出优异的电路级联潜力. 后续研究中, 可通过优化设计p-FET与n-FET的器件尺寸比例、推进器件尺寸微缩、制备高介电常数栅介质层等技术途径, 进一步提升电路性能.

-

本研究报道了一种基于一步热退火工艺的二维半导体极性调控的新策略. 经热退火, Pd-WSe2 FETs的极性发生转变, 其导电特性由n型主导转变为p型主导; 而Cr-WSe2 FETs在相同退火条件下则始终保持n型主导的导电特性. 基于此, 通过在同一WSe2上选择性制备不同金属作为源漏电极, 结合一步退火工艺实现了互补晶体管(p-FET/n-FET)的单片集成, 并通过器件互联构建了互补逻辑反相器. 所构建的反相器展现出优异性能, 其电压增益达23, 总噪声容限达2.3 V(0.92 Vdd). 本研究为二维半导体的极性调控提供了新的技术方案, 并为推进二维材料在后摩尔时代集成电路中的应用提供了助力.

一步退火工艺构建WSe2互补晶体管

One-step-annealing-process constructed WSe2 complementary transistors

-

摘要: 二维半导体材料凭借其独特的物理特性与优异的电学性能, 在后摩尔时代集成电路发展中展现出巨大潜力. 开发与二维材料兼容的极性调控方法, 已成为基于二维半导体构建互补逻辑电路、实现低功耗且高稳定性信息处理功能的关键, 有望为持续提升集成电路性能提供新路径. 本研究报道了一种基于一步退火工艺的二维半导体极性调控策略, Pd电极接触的WSe2晶体管的导电特性经退火由n型主导转变为p型主导; 而Cr电极接触的器件则始终保持n型主导的导电特性. 在此基础上, 通过在同一WSe2上选择性制备不同金属材料的源漏电极并结合一步退火工艺, 实现了互补晶体管的单片集成, 进而通过器件互联实现了反相器功能. 在2.5 V的电源电压(Vdd)下, 反相器增益达23, 总噪声容限达2.3 V(0.92 Vdd). 该研究为二维半导体的极性调控提供了全新的技术路径.Abstract: Two-dimensional (2D) semiconductor materials exhibit tremendous potential for post-Moore integrated circuits due to their unique physical properties and superior electrical characteristics. However, critical challenges in polarity modulation and complementary integration have significantly hindered the practical applications of 2D materials. The development of compatible polarity-modulation techniques has emerged as a critical step in achieving device functional integration for constructing 2D materials-based complementary circuits. This study innovatively proposes a one-step-annealing-driven polarity-modulation strategy for 2D semiconductors. It is demonstrated in this study that the conduction behavior of Pd-contacted WSe2 transistors transitions from n-type to p-type dominance after annealing, while Cr-contacted devices maintain n-type dominance. Based on this polarity-modulation strategy, by selectively fabricating source and drain electrodes with different metal materials (Pd and Cr) on the same WSe2, combined with a one-step annealing process, the monolithic integration of complementary transistors is achieved, thereby realizing inverter function through device interconnection. The fabricated inverters exhibit a high voltage gain of 23 and a total noise margin of 2.3 V(0.92 Vdd) at an applied Vdd of 2.5 V. This work not only establishes a novel technical pathway for polarity modulation in 2D materials but also provides crucial technological support for developing 2D semiconductor-based complementary logic circuits.

-

Key words:

- tungsten diselenide /

- polarity modulation /

- complementary transistors .

-

-

图 1 WSe2 FETs的极性调控 (a) 以Pd和Cr作为源漏接触电极的WSe2器件在退火前后的光学照片对比, 其中将退火前后Pd-WSe2与Cr-WSe2器件电极近邻沟道区域分别标记为区域Ⅰ, Ⅱ, Ⅲ和Ⅳ, 比例尺为1 μm; (b) 图(a)中对应区域“Ⅰ—Ⅳ”的拉曼光谱表征结果; 以Pd(c)和Cr(d)为源漏接触电极的背栅结构WSe2 FETs退火前后的转移特性曲线, 施加Vds为3 V, 器件结构示意图如插图所示

Figure 1. Polarity modulation of WSe2 FETs: (a) Comparative optical micrographs of Pd-contact and Cr-contact WSe2 devices before and after annealing. The electrode-proximal channel zones in Pd-WSe2 and Cr-WSe2 devices are labeled as regions Ⅰ, Ⅱ, Ⅲ and Ⅳ before and after annealing states, respectively, the scale bar is 1 μm. (b) Raman spectrum characterization results of the corresponding regions “Ⅰ–Ⅳ” marked in Figure (a). Transfer characteristic curves of back-gated WSe2 FETs with Pd contact (c) and Cr contact (d) before and after annealing, measured at Vds of 3 V, and the insets illustrate the schematics of device structures.

图 2 基于WSe2的互补FETs的单片集成与电学特性 (a) 在单一WSe2材料上集成互补FETs的器件结构示意图, 经退火操作后, Pd-WSe2 FET表现为p-FET, Cr-WSe2 FET表现为n-FET; (b) p-FET和n-FET的转移特性曲线, 其中红色曲线代表p-FET, 蓝色曲线代表n-FET, 施加的Vds分别为–1 V和1 V; p-FET(c)和n-FET(d)的输出特性曲线, Vg变化范围为0—2.5 V, 变化步长为0.5 V, 施加的Vs分别为3和0 V

Figure 2. Monolithic integration and electrical characteristics of WSe2-based complementary FETs: (a) Schematic of the integrated complementary FETs on a single WSe2 flake, the annealed Pd-WSe2 FET serves as p-FET and the Cr-WSe2 FET functions as n-FET; (b) transfer characteristic curves of the p-FET (red curve) and n-FET (blue curve), the applied Vds are –1 V and 1 V, respectively; output characteristic curves of the p-FET (c) and n-FET (d), the Vg swept from 0 to 2.5 V with step increments of 0.5 V, and the applied Vs are 3 and 0 V, respectively.

图 3 基于WSe2 FETs构建的互补逻辑反相器及其电学性能 (a) p-FET和n-FET串联组成的互补逻辑反相器的电路图; (b) 反相器的电压传输特性曲线, 所施Vdd范围为1—2.5 V, 变化步长为0.5 V; (c) 基于反相器电压传输特性曲线提取的电压增益; (d) 当Vdd为2.5 V时, WSe2反相器的蝶形电压传输特性曲线

Figure 3. Construction and electrical characteristics of complementary logic inverter based on WSe2 FETs: (a) Circuit diagram of the complementary logic inverter composed of p-FET and n-FET connected in series; (b) voltage transfer characteristic curves of inverter, the applied Vdd range from 1 to 2.5 V with step increments of 0.5 V; (c) voltage gain extracted from the voltage transfer characteristic curves of the inverter; (d) butterfly voltage transfer characteristic curves of WSe2 inverter at applied Vdd of 2.5 V.

-

[1] Desai S B, Madhvapathy S R, Sachid A B, Llinas J P, Wang Q X, Ahn G H, Pitner G, Kim M J, Bokor J, Hu C M, Wong H S P, Javey A 2016 Science 354 99 doi: 10.1126/science.aah4698 [2] Liu Y, Duan X D, Huang Y, Duan X F 2018 Chem. Soc. Rev. 47 6388 doi: 10.1039/C8CS00318A [3] Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A 2011 Nat. Nanotechnol. 6 147 doi: 10.1038/nnano.2010.279 [4] Wu F, Tian H, Shen Y, Hou Z, Ren J, Gou G Y, Sun Y B, Yang Y, Ren T L 2022 Nature 603 259 doi: 10.1038/s41586-021-04323-3 [5] Akinwande D, Huyghebaert C, Wang C H, Serna M I, Goossens S, Li L J, Wong H S P, Koppens F H L 2019 Nature 573 507 doi: 10.1038/s41586-019-1573-9 [6] Das S, Sebastian A, Pop E, McClellan C J, Franklin A D, Grasser T, Knobloch T, Illarionov Y, Penumatcha A V, Appenzeller J, Chen Z H, Zhu W J, Asselberghs I, Li L J, Avci U E, Bhat N, Anthopoulos T D, Singh R 2021 Nat. Electron. 4 786 doi: 10.1038/s41928-021-00670-1 [7] Jayachandran D, Pendurthi R, Sadaf M U K, Sakib N U, Pannone A, Chen C, Han Y, Trainor N, Kumari S, Mc Knight T V, Redwing J M, Yang Y, Das S 2024 Nature 625 276 doi: 10.1038/s41586-023-06860-5 [8] Sun X, Zhu C, Yi J, Xiang L, Ma C, Liu H, Zheng B, Liu Y, You W, Zhang W, Liang D, Shuai Q, Zhu X, Duan H, Liao L, Liu Y, Li D, Pan A 2022 Nat. Electron. 5 752 doi: 10.1038/s41928-022-00858-z [9] Xie M S, Jia Y Y, Nie C, Liu Z H, Tang A, Fan S Q, Liang X Y, Jiang L, He Z Z, Yang R 2023 Nat. Commun. 14 5952 doi: 10.1038/s41467-023-41736-2 [10] Yu J, Wang H, Zhuge F, Chen Z, Hu M, Xu X, He Y, Ma Y, Miao X, Zhai T 2023 Nat. Commun. 14 5662 doi: 10.1038/s41467-023-41363-x [11] Zhang Q, Wang X F, Shen S H, Lu Q, Liu X, Li H, Zheng J, Yu C P, Zhong X, Gu L, Ren T L, Jiao L 2019 Nat. Electron. 2 164 doi: 10.1038/s41928-019-0233-2 [12] Zhu K, Wen C, Aljarb A A, Xue F, Xu X, Tung V, Zhang X, Alshareef H N, Lanza M 2021 Nat. Electron. 4 775 doi: 10.1038/s41928-021-00672-z [13] Haynes T E, Eaglesham D J, Stolk P A, Gossmann H J, Jacobson D C, Poate J M 1996 Appl. Phys. Lett. 69 1376 doi: 10.1063/1.117441 [14] Pandey K C, Erbil A, Cargill I G, Boehme R F, Vanderbilt D 1988 Phys. Rev. Lett. 61 1282 doi: 10.1103/PhysRevLett.61.1282 [15] Cai J, Sun Z, Wu P, Tripathi R, Lan H Y, Kong J, Chen Z H, Appenzeller J 2023 Nano Lett. 23 10939 doi: 10.1021/acs.nanolett.3c03184 [16] Kim J K, Cho K, Jang J, Baek K Y, Kim J, Seo J, Song M, Shin J, Kim J, Parkin S S P, Lee J H, Kang K, Lee T 2021 Adv. Mater. 33 2101598 doi: 10.1002/adma.202101598 [17] Luo W, Zhu M J, Peng G, Zheng X M, Miao F, Bai S X, Zhang X A, Qin S Q 2018 Adv. Funct. Mater. 28 1704539 doi: 10.1002/adfm.201704539 [18] Qi D Y, Han C, Rong X M, Zhang X W, Chhowalla M, Wee A T S, Zhang W J 2019 ACS Nano 13 9464 doi: 10.1021/acsnano.9b04416 [19] Tosun M, Chuang S, Fang H, Sachid A B, Hettick M, Lin Y J, Zeng Y P, Javey A 2014 ACS Nano 8 4948 doi: 10.1021/nn5009929 [20] Yu L L, Zubair A, Santos E J G, Zhang X, Lin Y X, Zhang Y H, Palacios T 2015 Nano Lett. 15 4928 doi: 10.1021/acs.nanolett.5b00668 [21] Liu Y, Guo J, Zhu E, Liao L, Lee S J, Ding M, Shakir I, Gambin V, Huang Y, Duan X 2018 Nature 557 696 doi: 10.1038/s41586-018-0129-8 [22] Wang Y, Kim J C, Li Y, Ma K Y, Hong S, Kim M, Shin H S, Jeong H Y, Chhowalla M 2022 Nature 610 61 doi: 10.1038/s41586-022-05134-w [23] Pan C, Wang C-Y, Liang S-J, Wang Y, Cao T, Wang P, Wang C, Wang S, Cheng B, Gao A, Liu E, Watanabe K, Taniguchi T, Miao F 2020 Nat. Electron. 3 383 doi: 10.1038/s41928-020-0433-9 [24] Pang C S, Thakuria N, Gupta S K, Chen Z 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, December 1–5, 2018 pp22.2.1–22.2.4 [25] Resta G V, Balaji Y, Lin D, Radu I P, Catthoor F, Gaillardon P E, De Micheli G 2018 ACS Nano 12 7039 doi: 10.1021/acsnano.8b02739 [26] Guo Y, Li J, Zhan X, Wang C, Li M, Zhang B, Wang Z, Liu Y, Yang K, Wang H, Li W, Gu P, Luo Z, Liu Y, Liu P, Chen B, Watanabe K, Taniguchi T, Chen X-Q, Qin C, Chen J, Sun D, Zhang J, Wang R, Liu J, Ye Y, Li X, Hou Y, Zhou W, Wang H, Han Z 2024 Nature 630 346 doi: 10.1038/s41586-024-07438-5 [27] Kong L G, Zhang X D, Tao Q Y, Zhang M L, Dang W Q, Li Z W, Feng L P, Liao L, Duan X F, Liu Y 2020 Nat. Commun. 11 1866 doi: 10.1038/s41467-020-15776-x [28] Li R, Lu F, Deng J, Fu X, Wang W, Tian H 2024 J. Semicond. 45 012701 doi: 10.1088/1674-4926/45/1/012701 [29] Jobayr M R, Salman E M T 2023 J. Semicond. 44 032001 doi: 10.1088/1674-4926/44/3/032001 [30] Chou S A, Chang C, Wu B H, Chuu C P, Kuo P C, Pan L H, Huang K C, Lai M H, Chen Y F, Lee C L, Chen H Y, Shiue J, Chang Y M, Li M Y, Chiu Y P, Chen C W, Ho P H 2025 Nat. Commun. 16 2777 doi: 10.1038/s41467-025-57986-1 [31] Herrmann P, Klimmer S, Lettau T, Weickhardt T, Papavasileiou A, Mosina K, Sofer Z, Paradisanos I, Kartashov D, Wilhelm J, Soavi G 2025 Nat. Photonics 19 300 doi: 10.1038/s41566-024-01591-z [32] Oberoi A, Han Y, Stepanoff S P, Pannone A, Sun Y, Lin Y C, Chen C, Shallenberger J R, Zhou D, Terrones M, Redwing J M, Robinson J A, Wolfe D E, Yang Y, Das S 2023 ACS Nano 17 19709 doi: 10.1021/acsnano.3c03060 [33] Liu X, Shan J, Cao T, Zhu L, Ma J, Wang G, Shi Z, Yang Q, Ma M, Liu Z, Yan S, Wang L, Dai Y, Xiong J, Chen F, Wang B, Pan C, Wang Z, Cheng B, He Y, Luo X, Lin J, Liang S J, Miao F 2024 Nat. Mater. 23 1363 doi: 10.1038/s41563-024-01888-y [34] 拉贝艾简M著 (周润德译) 2004 数字集成电路—电路、系统与设计 (北京: 电子工业出版社) 第136—140页 {译著} Rabaey J M (translated by Zhou R D) 2004 Digital Integrated Circuits A Design Perspective (Beijing: Publishing House of Electrnics Industry) pp136–140 [35] Park Y J, Katiyar A K, Anh Tuan H, Ahn J H 2019 Small 15 1901772 doi: 10.1002/smll.201901772 -

首页

首页 登录

登录 注册

注册

下载:

下载: