-

横向双扩散金属氧化物半导体(LDMOS)因其高集成度、高频率和低导通电阻的特点, 成为功率半导体器件中的重要组成部分, 在电源管理, 汽车电子等领域得到广泛应用[1-5]. 由于传统的LDMOS器件的耐压主要由轻掺杂的漂移区来承担, 因此要实现高击穿电压(BV), 就需要降低器件漂移区掺杂浓度或增大漂移区的长度, 然而这两种方法均会增大器件的比导通电阻(Ron,sp). 因此, 器件的Ron,sp与BV之间存在矛盾关系[6-8].

为改善器件的Ron,sp与BV之间的矛盾关系, 一方面可以从材料出发, 采用SiC, GaN, Ga2O3等宽禁带半导体材料, 由于宽禁带材料具有更高的临界击穿电场, 因此在相同的掺杂条件下器件可以承受更高的电压[9,10], 但宽禁带半导体功率器件仍不适用于功率集成电路, 因其难以与硅基CMOS集成; 另一方面则是从器件结构出发, 采用减小表面电场技术(RESURF)[11-13]、横向变掺杂技术(VLD)[14,15]、埋层[16,17]和超结[18,19]等方法来优化器件内部结构, 实现优异的器件性能, 打破硅极限, 但以上结构主要适用于单沟道器件. 此外, 有相关研究报道了具有多数载流子积累的LDMOS器件, 通过引入半绝缘多晶硅(SIPOS)场板等结构使得在漂移区中形成较高浓度的电子积累层来降低器件的导通电阻, 实现器件Ron,sp与BV之间的良好折中[20,21]. 但是, 积累型器件导通时存在较多的自由载流子将显著降低器件的关断特性, 进而影响器件的开关频率, 不利于器件性能的进一步提升.

本文提出了一种具有P/N纵向交替的双漂移区(PND)以及双导通路径(DP)的LDMOS结构(PND-DP LDMOS). 通过引入平面栅结构, 在对其施加正向电压VG时, P型漂移区表面发生反型, 形成能够连接沟道和N+漏极的高浓度电子反型层, 从而提高导通时的电子密度, 有效降低器件导通电阻; 通过引入槽型栅结构, 使得器件能够在N型漂移区和P型漂移区分别形成独立的导通路径, 从而产生一条额外的电子消失路径, 提高器件的关断特性. 为验证本文所提出器件的输出特性、击穿特性和关断特性等电学特性, 本文采用Sentaurus TCAD软件[22]对其进行仿真模拟, 仿真中所用到的物理模型包括: 迁移率模型(Doping Dependence, HighFieldSaturation, Enormal)、不完全电离模型、禁带宽度模型(Slotboom)、载流子复合模型(Shockley-Read-Hall, Auger)以及雪崩击穿模型(Okuto avalanche generation). 仿真结果表明, PND-DP LDMOS在实现低导通电阻的同时缩短了器件的关断时间(toff), 实现优异的器件性能.

-

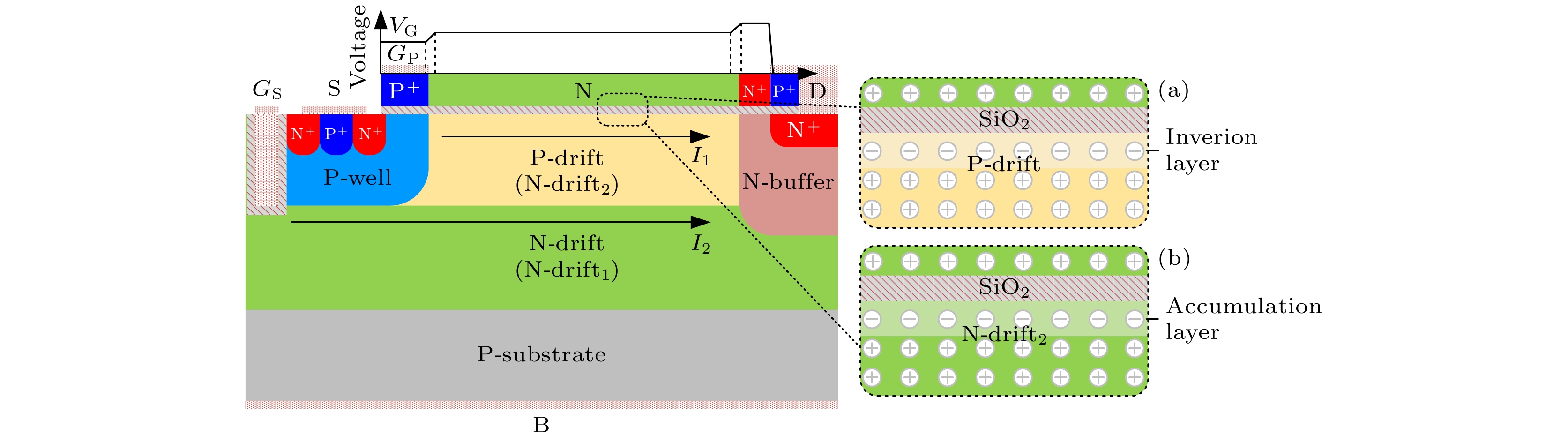

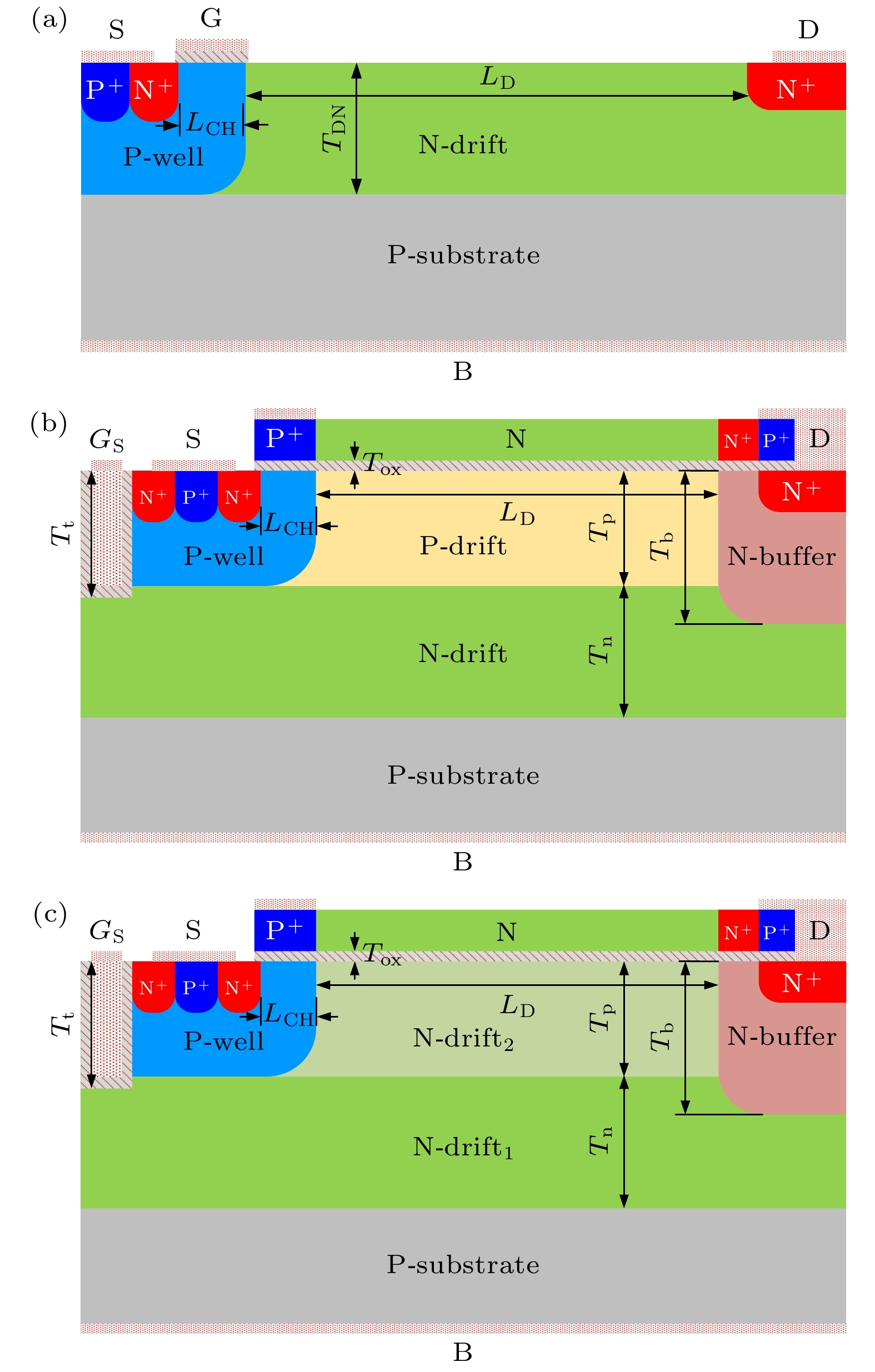

PND-DP LDMOS的器件结构如图1(b)所示, 其与图1(a)所示的传统LDMOS(Conv. LDMOS)的区别在于引入了平面栅和槽型栅所构成的双栅结构以及N/P交替的双漂移区结构. 平面栅可实现对器件导通时电子浓度的调控, 对其施加正向电压时, 器件表面的顶层硅与P型漂移区之间产生一个电势差ΔV, 使得P型漂移区表面发生反型, 形成连接沟道和N+漏区的高浓度电子反型层, 从而提高导通时的电子密度, 显著降低器件Ron,sp. 槽型栅极的引入可使器件在关断时会产生一条额外的电子消失路径, 从而缩短器件的toff. 此外, 由于采用了P型漂移区, 电子在其内部输运时与空穴发生复合, 加快了电子的消失过程, 进一步缩短了器件的toff. 在N+漏区下方引入N型缓冲层, 一方面其可以接收槽型栅极所控制的电流到漏极, 另一方面可以调制器件的纵向电场, 提升器件的纵向耐压能力. 为了讨论漂移区类型对器件性能的影响, 本文提出的另一种具有双导通路径的积累型LDMOS结构(NND-DP LDMOS), 其与PND-DP LDMOS的区别在于, PND-DP LDMOS的漂移区为N型和P型纵向交替的结构, 而NND-DP LDMOS为双N型漂移区, 如图1(c)所示. 图2所示为两种器件的工作机理, 由于双漂移区、槽型栅和平面栅的引入, 使得器件可以形成两条电子的导通和消失路径(I1, I2). 但两者的I1所产生的机理不同, 对于PND-DP LDMOS其I1的产生的机理为反型, 如图2(a)所示. 而NND-DP LDMOS为积累, 如图2(b)所示. 优化后的传统LDMOS器件(CONV LDMOS)与本文所提出的PND-DP LDMOS和NND-DP LDMOS器件的参数如表1所示.

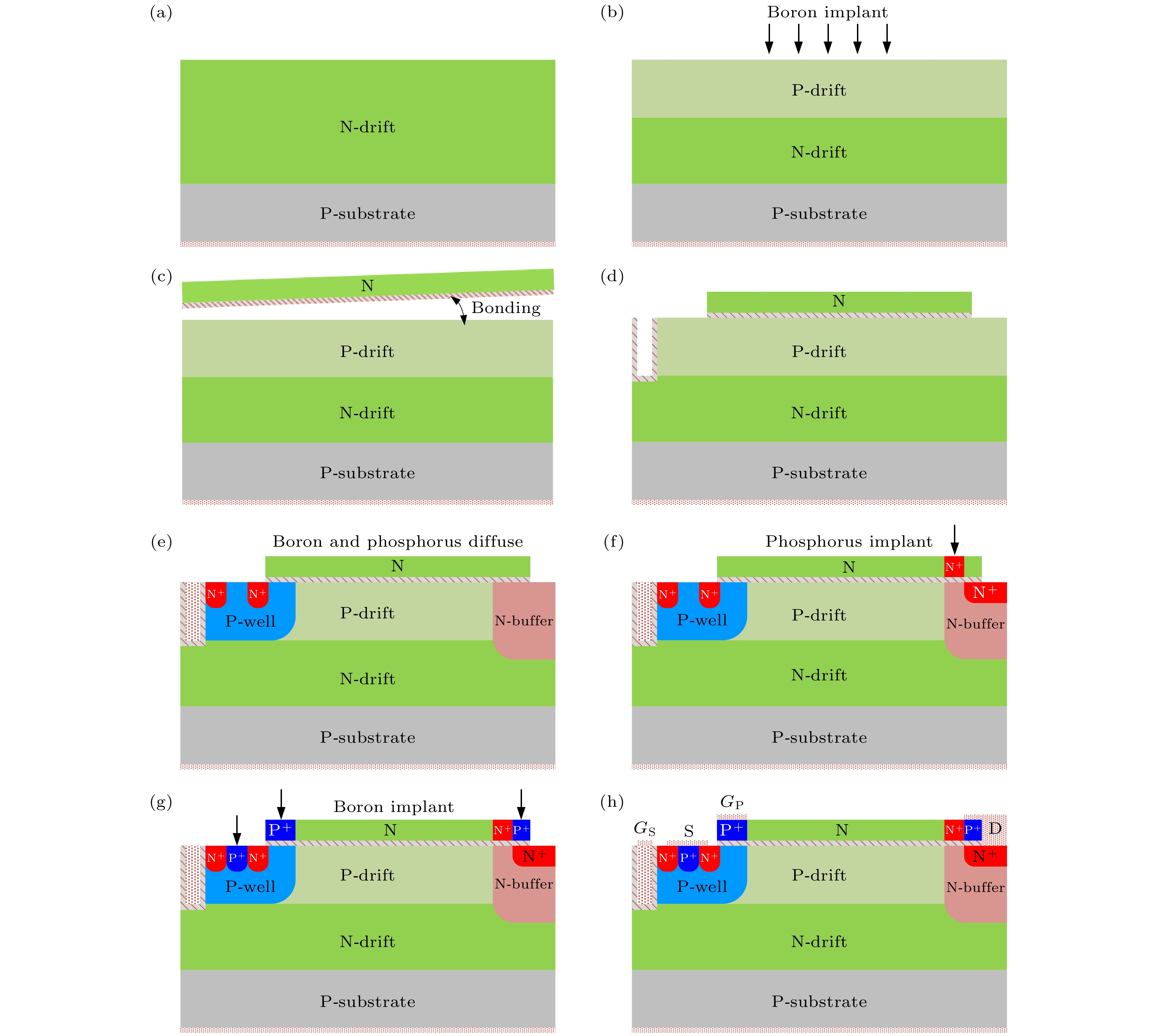

图3所示为制备PND-DP LDMOS器件的工艺流程. 选择P型硅衬底并外延N型外延层形 成N型漂移区(图3(a)). 在外延层表面注入硼离子形成P型漂移区(图3(b)). 通过氧注入隔离技术或直接键合技术制作薄层的硅衬底(图3(c)). 通过选择性刻蚀, 刻蚀出源漏的位置. 刻蚀出硅槽并在其内部热生长一层二氧化硅栅介质层(如图1(d)所示). 利用双扩散技术形成沟道, 并在漏极区域扩散形成N型缓冲层(图3(e)). 在N型顶层硅中离子注入形成N+区以阻挡器件导通时顶层硅中的空穴电流(图3(f)). 通过离子注入分别在顶层硅和Pwell中形成P+区(图3(g)). 在源极、漏极、平面栅极和槽型栅极区域淀积金属(图3(h)).

-

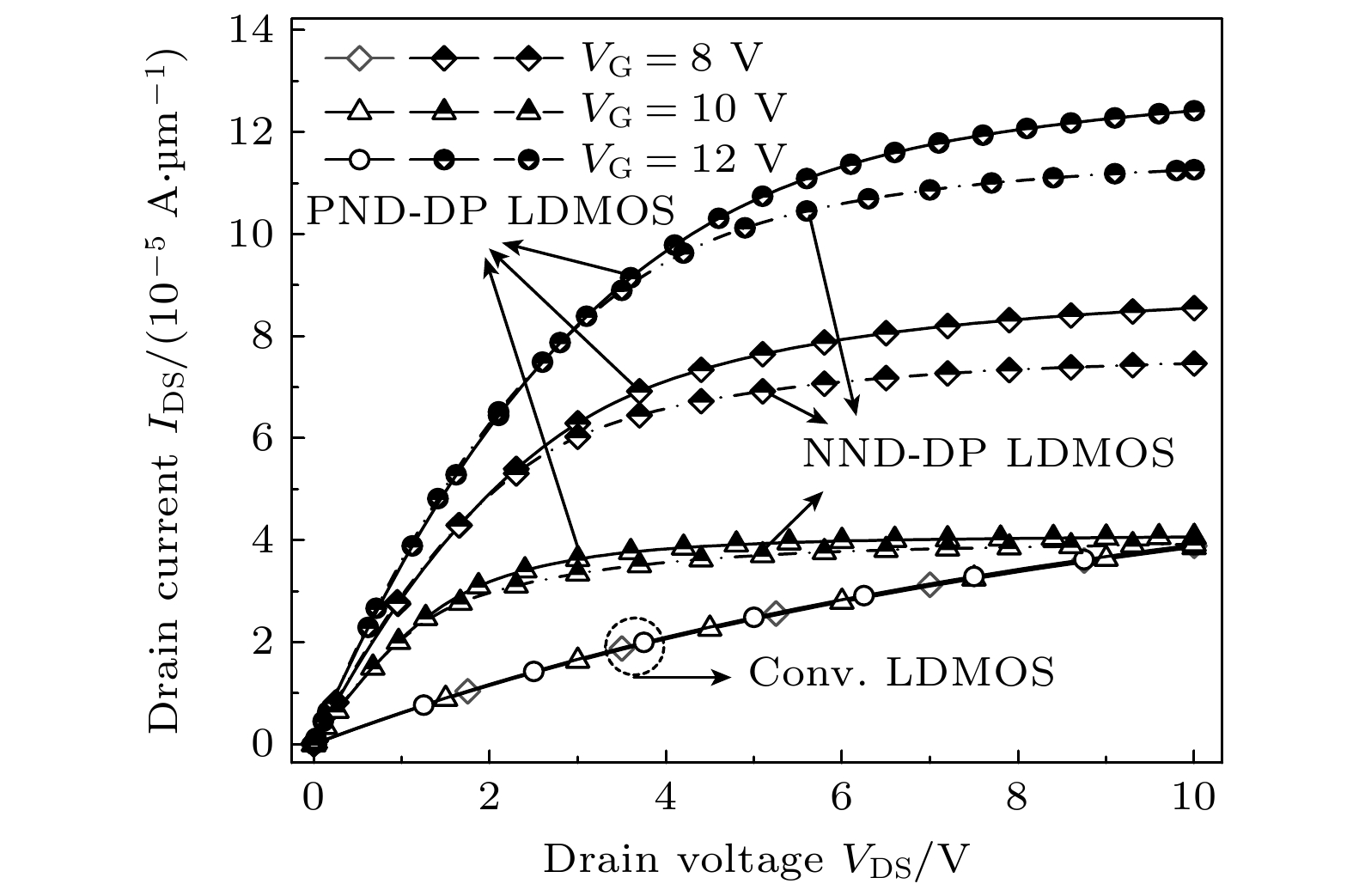

图4所示为本文所提出器件与传统器件的输出特性曲线. 可以看到, 在相同的栅极电压下(VG), 本文所提出的PND-DP LDMOS和NND-DP LDMOS器件输出特性曲线的斜率明显大于传统的LDMOS, 表明本文所提出的器件具有更小的导通电阻, 且具有更高的饱和电流. 这是因为平面栅的引入, 当施加正向的栅极电压时, 顶层多晶硅会传导栅极的电势, 使得所提出器件的漂移区表面的顶层硅也会具有较高的电势, 从而P型漂移区(N型漂移区)体内的电子会被牵引到表面, 反型(积累)出一层连接源区和漏区的高浓度的电子薄层, 其浓度可达到1017 cm–3, 远高于传统器件导通时的电子密度, 因此所提出器件具有较高的饱和电流以及超低的Ron,sp.

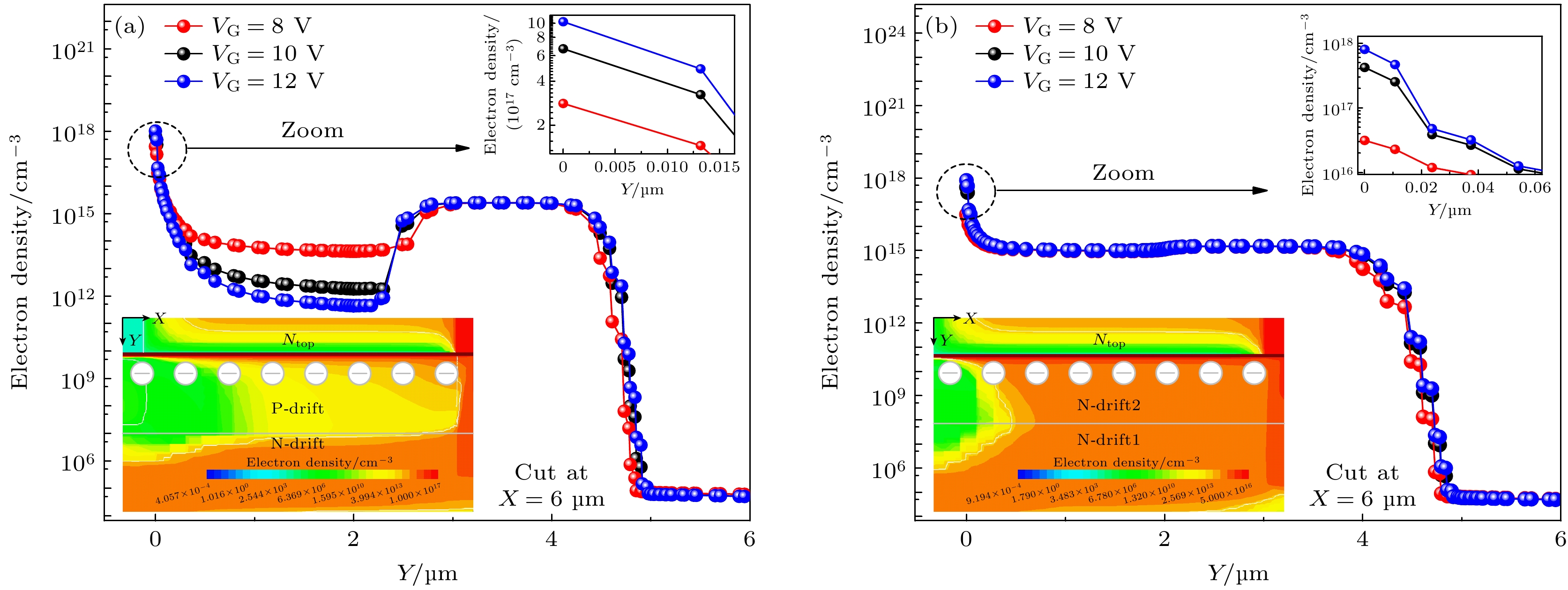

图5所示为PND-DP LDMOS和NND-DP LDMOS器件的电子分布图. 器件漂移区的表面形成了极高浓度的电子层, 其浓度远高于体内的电子浓度. 此外, 栅极电压可对其浓度进行调控, 随着VG的增大, 漂移区表面的电子浓度也随之提高. 当VG由8 V增大到12 V, PND-DP LDMOS漂移区表面的电子浓度由3×1017 cm–3提高到1×1018 cm–3, Ron,sp从4.53 mΩ·cm2降低到2.41 mΩ·cm2, 减小了47%. 因此PND-DP LDMOS和NND-DP LDMOS的导通状态与VG的变化密切相关, 其栅极对器件导通性能的调控作用明显高于传统器件.

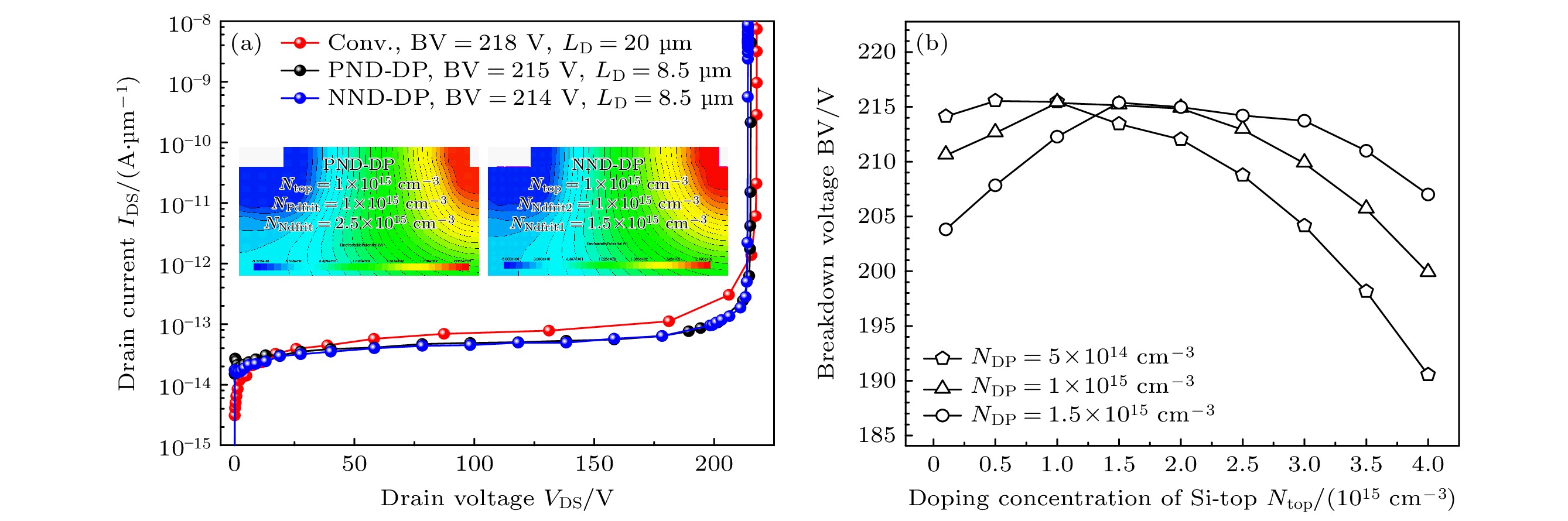

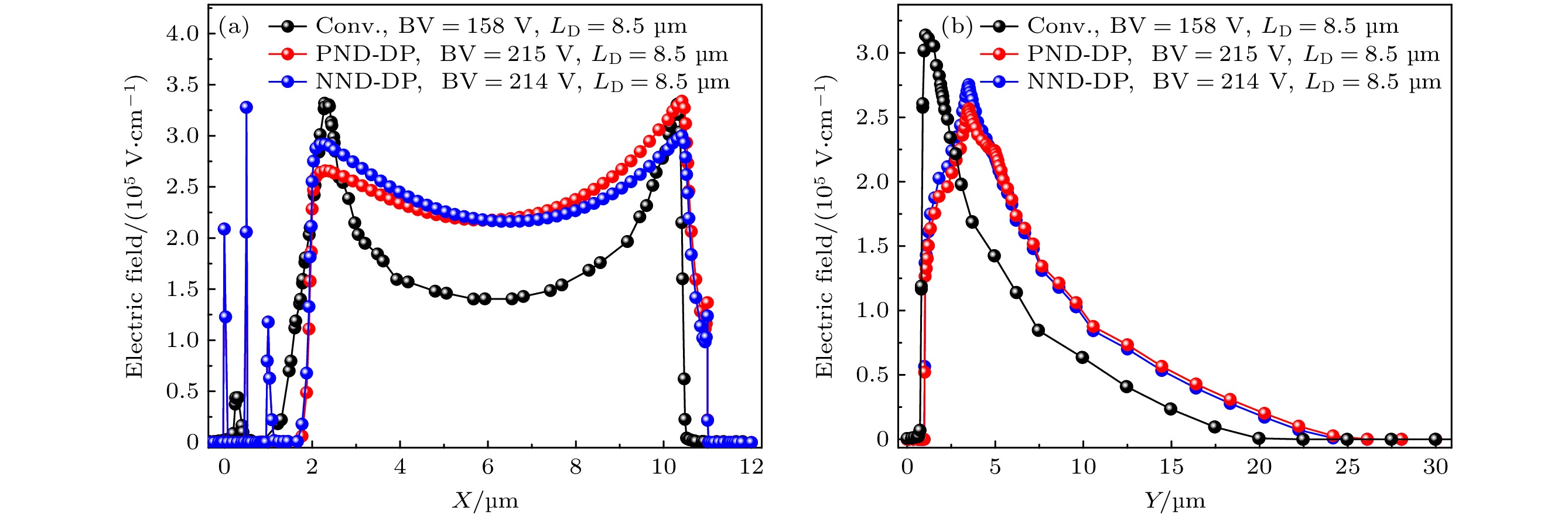

图6所示为器件的电压击穿曲线. 在相同的200 V耐压等级下, PND-DP LDMOS和NND-DP LDMOS器件相比于传统的LDMOS具有更短的漂移区长度. 这是因为顶层硅会对其下方区域进行电场调制, 使得表面电场分布更为均匀. 从图7(a)可以看到, PND-DP LDMOS和NND-DP LDMOS器件的表面电场分布相对于Conv. LDMOS更趋近于一个矩形(理想的电场分布). 从图6(b)可以看到, BV的峰值在顶层硅掺杂浓度与其下方的漂移区掺杂浓度相近时得到, 此时顶层硅和漂移区的电势线基本垂直于器件表面且分布地更为均匀, 如图6(a)所示. 此外, N型缓冲层的引入一方面其可以接收槽型栅极所控制的电流到漏极, 另一方面可以调制器件的纵向电场, 如图7(b)所示, 相比于Conv. LDMOS, PND-DP LDMOS和NND-DP LDMOS的纵向电场峰值由表面移动到了体内, 提高了器件的纵向耐压能力.

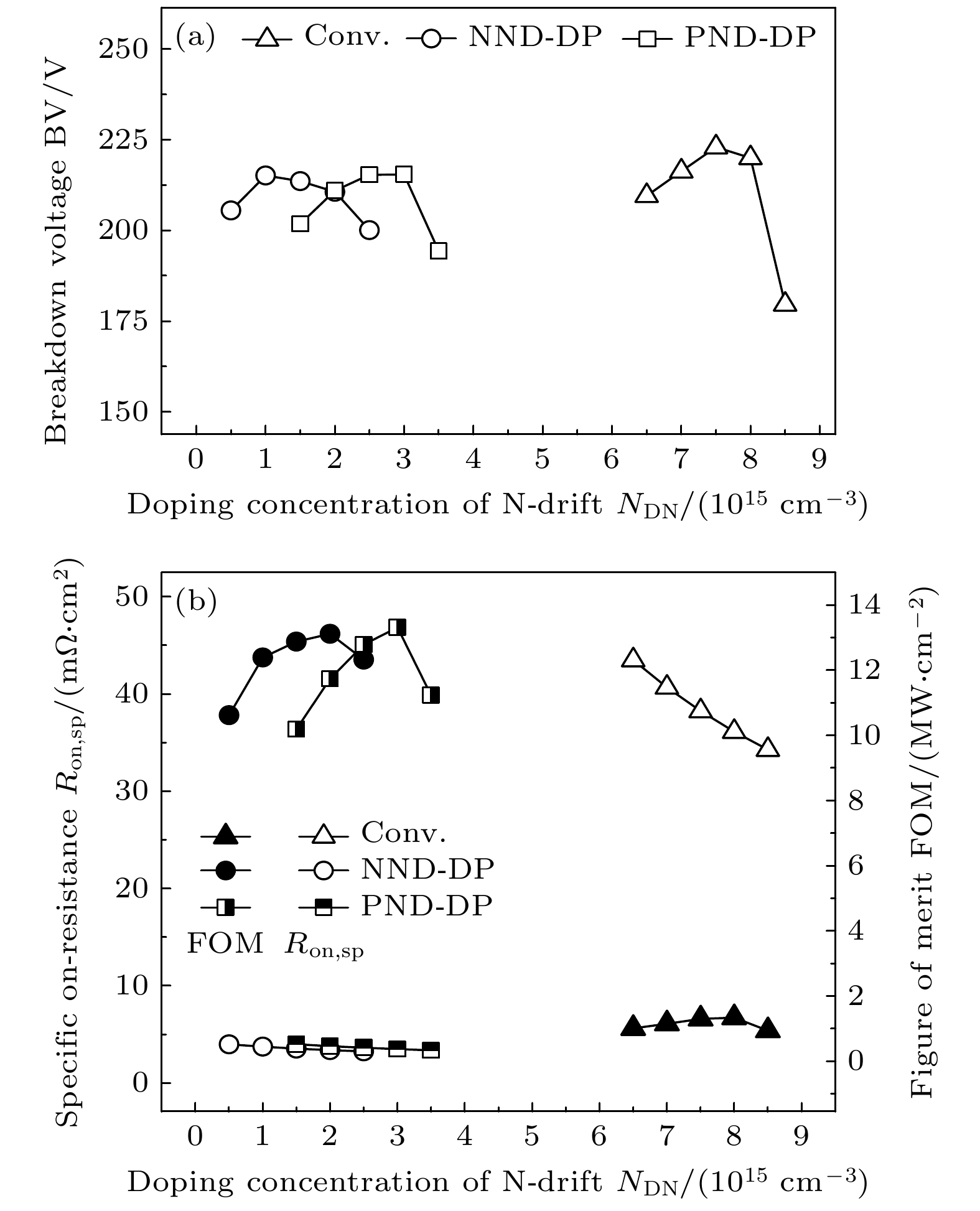

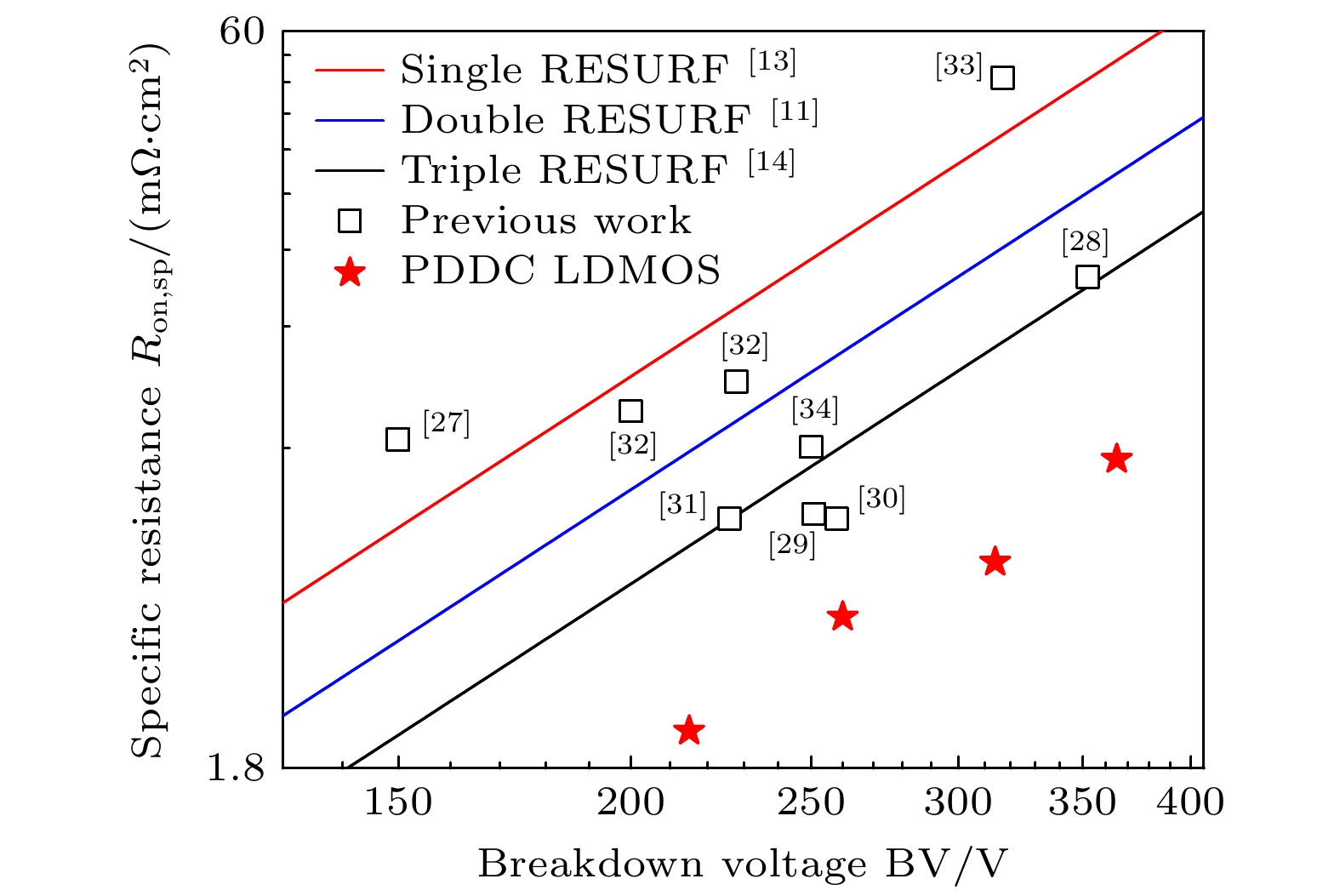

图8所示为N型漂移区掺杂浓度(NDN)对器件导通电阻、击穿电压的影响. 可以看到, Conv. LDMOS, PND-DP LDMOS和NND-DP LDMOS的Ron,sp和BV随着NDN的增大均呈现先增大后减小的趋势. 从图8(a)可以看到, 在BV等级为200 V的情况下, PND-DP LDMOS和NND-DP LDMOS具有更小的NDN. NND-DP LDMOS的NDN相比于PND-DP LDMOS的更小, 这是因为PND-DP LDMOS的漂移区为N/P纵向交替结构, 上方的P型漂移区可以辅助耗尽其下方的N型漂移区, 因此PND-DP LDMOS最终优化后的NDN略大. 从图8(b)可以看到, 尽管PND-DP LDMOS和NND-DP LDMOS的NDN掺杂远小于Conv. LDMOS, 但其仍具有超低的Ron,sp且其随NDN的变化波动不大, 这是因为这两个器件的Ron,sp主要依赖于VG的控制, 有效削弱了器件Ron,sp对漂移区掺杂的依赖, 得到了更高的FOM(figure of merit, FOM = BV2/Ron,sp)[23–26]. 当LD为8.5 μm, VG为10 V时, PND-DP LDMOS和NND-DP LDMOS的BV为215和214 V, Ron,sp为3.43, 3.38 mΩ·cm2, FOM为13.31 MW/cm2, 13.11 MW/cm2. 与相同耐压等级的Conv. LDMOS相比, Ron,sp分别降低了90%, 91%, FOM提高了10倍. 图9和表2展示了本文提出的PND-DP LDMOS与其他器件[27–34]Ron,sp-BV的对比及其具体参数, 可以看到PND-DP LDMOS远优于Triple RESURF, 其进一步证明了本文所提出器件在Ron,sp和BV之间实现了优异的折中关系.

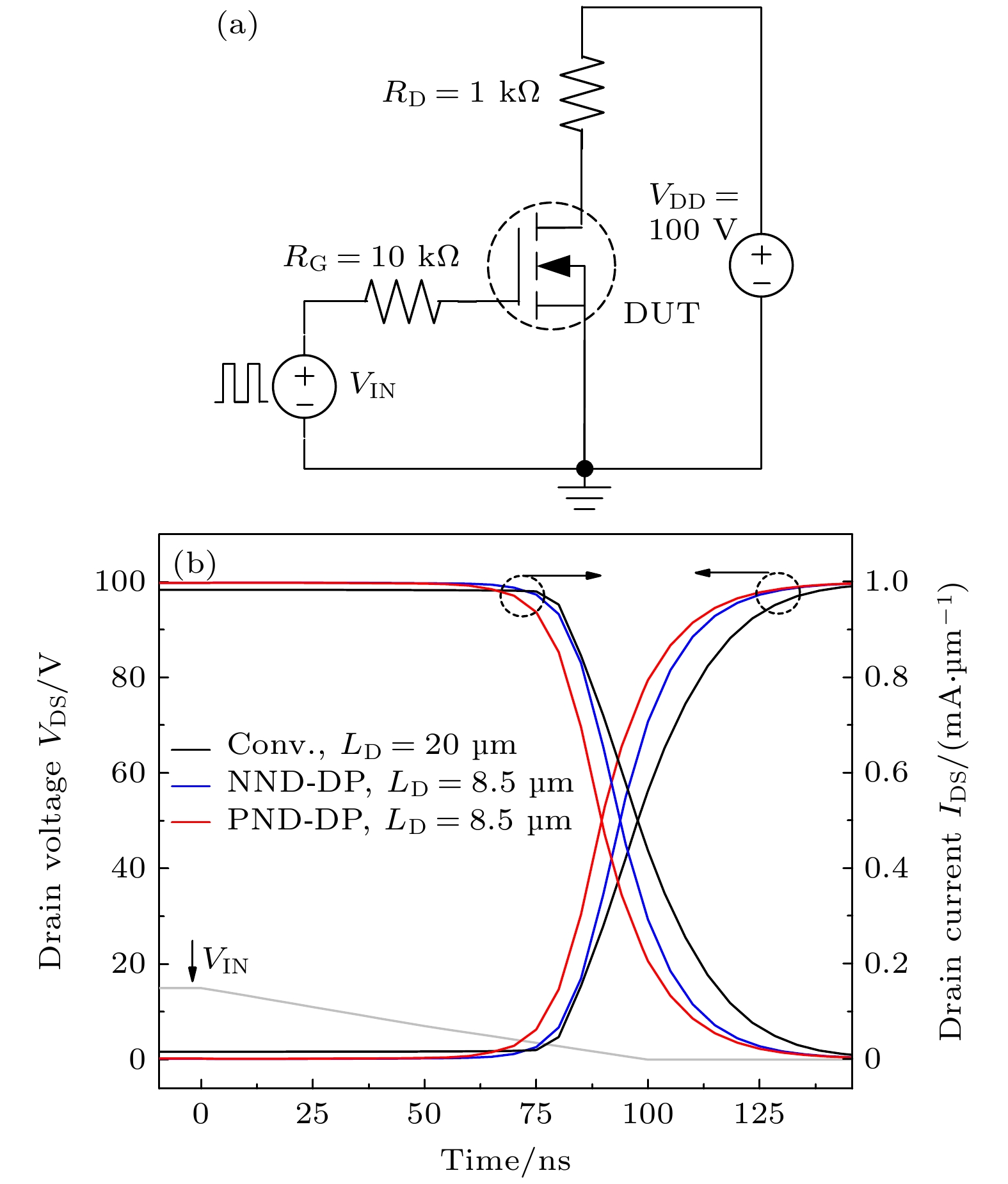

在仿真中, 采用图10(a)所示的电路研究了3种器件的关断特性. 图10(b)为仿真所得到的关断特性曲线. 可以看到, PND-DP LDMOS和NND-DP LDMOS的相比于Conv. LDMOS具有更短的关断时间. 这是因为, 其漂移区采用双漂移区以及双栅的结构, 使器件在关断时可产生一条额外的电子消失路径, 从而加快了电子的消失, 此外, 从图10(b)可以看到PND-DP LDMOS的关断特性优于NND-DP LDMOS, 这是因为PND-DP LDMOS第2个漂移区为P型, 使得电子在P型漂移区内输运时与空穴发生复合, 从而进一步地缩短了PND-DP LDMOS的toff. 相比于Conv. LDMOS, PND-DP LDMOS和NND-DP LDMOS的toff分别减小了11.6%, 8.0%.

-

本文提出了一种具有双漂移区和双导通路径的新型LDMOS器件, 通过N型和P型纵向交替的双漂移区结构、槽型栅和平面栅构成的双栅设计, 使得器件可以在漂移区内产生了两条独立的电子导通和消失路径, 在实现了器件Ron,sp和BV之间的优异折中的同时缩短了器件的关断时间. 为了讨论所以引入双漂移区的类型对器件性能的影响并与PND-DP LDMOS进行对比, 提出了NND-DP LDMOS, 从仿真结果可以看到, 两者的Ron,sp和BV的差别不大, 但PND-DP LDMOS具有更好的关断特性. LD为8.5 μm, VG为10 V时, PND-DP LDMOS的BV, Ron,sp和toff分别为215 V, 3.43 mΩ·cm², 9 ns, 相较于Conv. LDMOS器件导通电阻降低了90%, 关断时间缩短了11.6%.

具有超低比导通电阻的双漂移区双导通路径新型横向双扩散金属氧化物半导体

A novel LDMOS with dual-drift region and dual-conduction path with ultra-low specific on-resistance

-

摘要: 本文提出了一种具有双漂移区和双导通路径的新型横向双扩散金属氧化物半导体(LDMOS)器件, 实现了超低比导通电阻(Ron,sp). 其漂移区采用P型和N型纵向交替所构成的双漂移区结构, 并引入平面栅和槽型栅分别控制P型和N型漂移区, 使得器件能够在漂移区中形成两条独立的电子导通或消失路径. 在对平面栅施加正向电压时, 可使P型漂移区的表面发生反型, 形成连接沟道和N+漏极的高浓度电子反型层, 从而极大提高器件导通时的电子密度, 降低比导通电阻. 槽型栅极的引入可使器件在关断时产生一条额外的电子消失路径, 从而缩短器件的关断时间(toff). 此外, 由于引入P型漂移区, 使得电子在P型漂移区内输运时与其体内的空穴发生复合, 从而加快了电子的消失过程并进一步地缩短器件的toff. 仿真结果表明, 在200 V的击穿电压(BV)等级下, 本文所提出的新型LDMOS的Ron,sp为3.43 mΩ·cm2, 关断时间为9 ns. 相比传统的LDMOS器件, Ron,sp和toff分别下降了90%和11.6%. 该器件不仅实现了Ron,sp和BV的良好折中, 而且缩短了器件的toff, 展现出了优异的器件性能.Abstract: In order to improve the contradictory between specific on-resistance (Ron,sp) and breakdown voltage (BV) of lateral double-diffused metal oxide semiconductor (LDMOS) and enhance the turn-off characteristic, this paper proposes a novel LDMOS device with dual-drift regions and dual-conduction paths, which achieves an ultra-low Ron,sp. The key feature of the proposed device is the introduction of a dual-drift region structure with alternating P-type and N-type regions, combined with planar and trench gates to control the P-type and N-type drift regions, respectively. This configuration enables the formation of two independent electron conduction paths within the drift region. When a positive voltage is applied to the planar gate, a voltage difference is generated between the surface of the P-type drift region and the body of device’s drift. Therefore, under the influence of the voltage difference, the electrons are pulled to the surface of the P-type drift region to invert and form a high-density electron inversion layer that connects the channel and the N+ drain, significantly increasing the electron density during conduction and reducing the Ron,sp. The introduction of the trench gate provides an additional electron disappearance path, which shortens the device's turn-off time (toff). Furthermore, the introduction of the P-type drift region facilitates the recombination of electrons with holes within the P-type drift region, accelerating the electron disappearance process and further reducing the device’s toff. Furthermore, the proposed device exhibits a more uniform electric field distribution and higher voltage capability is due to the P+N-N+P+ structure adopted in the PolySi-top layer. During the off-state, both the P+N- junctions and the N+P+ junctions generate electric field peaks at the interfaces. These peaks modulate the electric field distribution across the surface of the drift region. Simulation results indicate that at the BV with a level of 200V, the proposed LDMOS exhibits an Ron,sp of 3.43 mΩ·cm² and a toff of 9 ns. Compared with conventional LDMOS devices, the proposed LDMOS possesses a 90% reduction in Ron,sp and an 11.6% decrease in toff. The proposed device not only achieves an excellent trade-off between Ron,sp and BV but also shortens the toff, demonstrating that the device achieves superior performance.

-

Key words:

- dual-drift /

- dual-conduction paths /

- specific on-resistance /

- breakdown voltage .

-

-

表 1 器件仿真中的关键参数

Table 1. Key parameters of devices’ simulation.

参数符号 参数含义 传统 PND-DP NND-DP Tox/μm 氧化层厚度 0.1 0.1 0.1 LD/μm 漂移区长度 20 8.5 8.5 TDP/TDN2/μm P-drift(N-drift2)的厚度 2 2 2 TDN/TDN1/μm N-drift(N-drift1)的厚度 — 3 3 Tb/μm N-buffer的厚度 — 3.5 3.5 LCH/μm 沟道长度 1.5 1.5 1.5 Tt/μm 槽栅的深度 — 2.1 2.1 NDP/NDN2/cm–3 P-drift(N-drift2)的掺杂浓度 — 1×1015 1×1015 NDN/NDN1/cm–3 N-drift(N-drift1) 的掺杂浓度 7.5×1015 2.5×1015 1.5×1015 Ntop/cm–3 N-top的掺杂浓度 — 1×1015 1×1015 Nsub/cm–3 衬底的掺杂浓度 3×1014 3×1014 3×1014 表 2 PND-DP LDMOS与其他器件的Ron,sp, BV, FOM

Table 2. Ron,sp, BV, and FOM of PND-DP LDMOS compared with other devices.

-

[1] Kong M, Yi B, Zhang B 2019 IEEE T. Electron. Dev. 66 592 doi: 10.1109/TED.2018.2882016 [2] Disney D, Chan W, Lam R, Blattner R, Ma S, Seng W, Chen J W, Cornell M, Williams R 2008 20th International Symposium on Power Semiconductor Devices and IC’s Orlando, FL, USA, May 18–22, 2008 pp24–27 [3] Sun W, Shi L, Sun Z, Yi Y, Li H, Lu S 2006 IEEE T. Electron. Dev. 53 891 doi: 10.1109/TED.2006.870536 [4] Erlbacher T, Bauer A J, Frey L 2010 IEEE Electron Device Lett. 31 464 doi: 10.1109/LED.2010.2043049 [5] Qiao M, Li Y, Zhou X, Li Z, Zhang B 2014 IEEE Electron Device Lett. 35 774 doi: 10.1109/LED.2014.2326185 [6] Baliga B J 2001 Proc. IEEE 89 822 doi: 10.1109/5.931471 [7] Efland T R, Tsai C Y, Pendharkar S 1998 International Electron Devices Meeting 1998 San Francisco, CA, USA, December 6–9, 1998 pp679–682 [8] Li M, Chen D, Jung D S, Shi X 2019 2019 China Semiconductor Technology International Conference Shanghai, China, March 17–18, 2019, pp1–3 [9] Baliga B J 2023 Springer Handbook of Semiconductor Devices (Cham: Springer Nature) pp491–523 [10] Baliga B J 2019 Fundamentals of Power Semiconductor Devices (Cham: Springer International Publishing [11] Appels J A, Vaes H M J 1979 1979 International Electron Devices Meeting December, 1979, pp238–241 [12] Hossain Z 2008 2008 20th International Symposium on Power Semiconductor Devices and IC’s Orlando, FL, USA, May 18–22, 2008 pp133–136 [13] Xiarong H, Bo Z, Xiaorong L, Guoliang Y, Xi C, Zhaoji L 2011 J. Semicond. 32 074006 doi: 10.1088/1674-4926/32/7/074006 [14] Hardikar S, Tadikonda R, Green D W, Vershinin K V, Narayanan E M S 2004 IEEE T. Electron. Dev. 51 2223 doi: 10.1109/TED.2004.839104 [15] Stengl R, Gosele U 1985 1985 International Electron Devices Washington, DC, USA, December 1–4, 1985 pp154–157 [16] Duan B, Xing L, Wang Y, Yang Y 2022 IEEE T. Electron. Dev. 69 658 doi: 10.1109/TED.2021.3134602 [17] Chen Y, Hu S, Cheng K, Jiang Y, Luo J, Wang J, Tang F, Zhou X, Zhou J, Gan P 2016 Micro. Nanostructures 89 59 [18] Fujihira T 1997 Jpn. J. Appl. Phys. 36 6254 doi: 10.1143/JJAP.36.6254 [19] Chen X B 2000 Chin. J. Electron. 9 6 [20] Baliga B J, Syau T, Venkatraman P 1992 IEEE Electron Device Lett. 13 427 doi: 10.1109/55.192780 [21] Wang Y D, Duan B X, Song H T, Yang Y T 2021 IEEE T. Electron. Dev. 68 2414 doi: 10.1109/TED.2021.3066085 [22] Inc. Synopsys 2016 SentaurusTM Device User Guide Verison L-2016.03 [23] Chen W Z, Qin H F, Zhang H S, Han Z S 2022 IEEE T. Electron. Dev. 69 1900 doi: 10.1109/TED.2022.3147731 [24] Zhou K, Luo X R, Li Z J, Zhang B 2015 IEEE T. Electron. Dev. 62 3334 doi: 10.1109/TED.2015.2466694 [25] Cao Z, Sun Q, Zhang H W, Wang Q, Ma C F, Jiao L C 2022 Micromachines 13 843 doi: 10.3390/mi13060843 [26] Cheng J, Zhang B, Li Z 2008 IEEE Electron Device Lett. 29 645 doi: 10.1109/LED.2008.922731 [27] Chen Y M, Lee C L, Tsai M H, Lee C T, Wang C C 2018 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs Chicago, IL, USA, May 13–17, 2018 pp331–334 [28] Zhang S, Tuan H C, Wu X J, Shi L, Wu J 2016 Microelectron. Reliab. 61 125 doi: 10.1016/j.microrel.2015.11.004 [29] Chen W, Pjencak J, Agam M, Janssens J, Jerome R, Menon S, Griswold M 2021 2021 33rd International Symposium on Power Semiconductor Devices and ICs Nagoya, Japan, May 30–June 03, 2021 pp287–290 [30] Qiao M, Liu W, Yuan L, Xu P, Ma C, Lin F, Liu K, Guo Y, Lin Z, Zhang S, Zhang B 2022 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs Vancouver, BC, Canada, May 22–25, 2022 pp149–152 [31] Kong M, Yi B, Chen X 2019 2019 IEEE 13th International Conference on Power Electronics and Drive Systems Toulouse, France, July 09–12, 2019 pp1–4 [32] Fan J, Wang Z G, Zhang B, Luo X R 2013 Chin. Phys. B 22 048501 doi: 10.1088/1674-1056/22/4/048501 [33] Honarkhah S, Nassif-Khalil S, Salama C A T 2004 Proceedings of the 30th European Solid-State Circuits Conference Leuven, Belgium, September 23, 2004 pp117–120 [34] Hölke A, Antoniou M, Udrea F 2020 2020 32nd International Symposium on Power Semiconductor Devices and ICs Vienna, Austria, September 13–18, 2020 pp435–438 -

首页

首页 登录

登录 注册

注册

下载:

下载: