-

与传统平面场效应晶体管(MOSFET)相比,具有超薄沟道的三维器件结构表现出许多优点,比如更好的短沟道效应抑制特性、更低工作电压、更低功耗等[1-4]。目前最具有应用前景的器件是水平堆叠环栅纳米片(GAA NS)晶体管,具有优秀的栅控能力,并在3 nm以下纳米节点具有较强的微缩能力,但同时也面临一系列的挑战[5]。对于水平堆叠纳米片器件,其中挑战之一就是内侧墙的制备[6],内侧墙的作用为调控栅极与源/漏极间的寄生电容与寄生电阻,并在栅极与源极/漏极(S/D)间充当沟道释放的刻蚀停止层来控制有效栅长,内侧墙的厚度和形貌显著影响上述作用效果,而决定内侧墙厚度及形貌的工艺为空腔刻蚀(cavity etching)。

目前公开报道的空腔刻蚀方法主要有三类:分别是湿法、气态法和干法。湿法主要是H2O2、HNO3、CH3COOH、HF等的混合溶液,其特点是选择比高,但是由于溶液反应的特点,存在毛细管效应和刻蚀剖面的“月牙”形等问题[7-9],局限了其应用。HCl气态法需要较高的反应温度增加了器件的热预算,且通常存在晶向选择性而无法获得理想的刻蚀剖面[10]。干法刻蚀在小尺寸、减弱“月牙”状以及提高刻蚀精度上具有优势,但是公开报道的干法刻蚀都是基于远程等离子(Remote plasma)源的刻蚀设备来实现工艺,其硬件复杂性相对常规干法刻蚀更高[11-13]。2021年IBM报道在6 nm的空腔,采用干法刻蚀工艺得到小于1 nm的硅损伤,且内侧墙轮廓较好,但是具体工艺方法并未公开报道[14],此外针对空腔刻蚀的实现方法以及相关机理也鲜有报道。

2019年中国科学院微电子研究所李俊杰提出了一种基于常规ICP进行SiGe/Si叠层准各向同性选择性干法刻蚀新方案,通过采用合适气体比例的CF4/O2/He体系获得了较为理想的刻蚀效果[15],但是并未对激励射频(SRF)功率,气压等工艺参数对刻蚀影响进行报道。本论文主要针对上述问题进行补充研究,并且对刻蚀前清洗等工艺对于刻蚀深度,“月牙”形貌控制,表面粗糙度及刻蚀精度影响与机制进行了探讨,最终获得了具有应用前景的内侧墙空腔刻蚀方案。

-

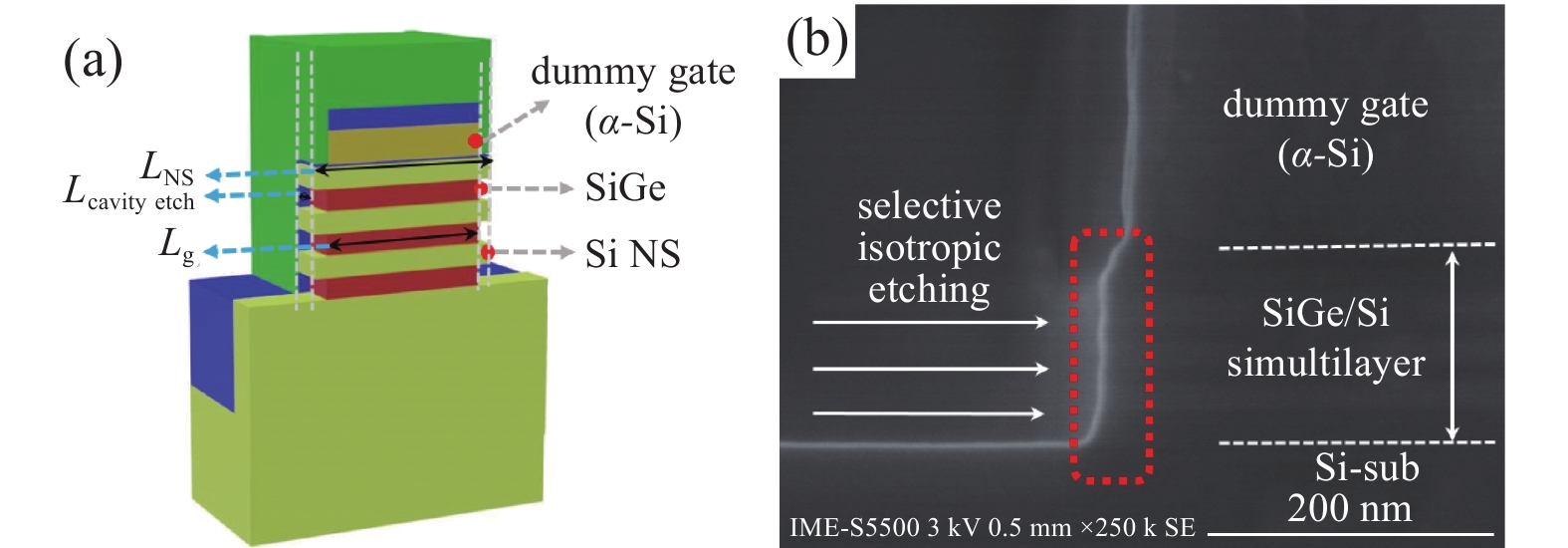

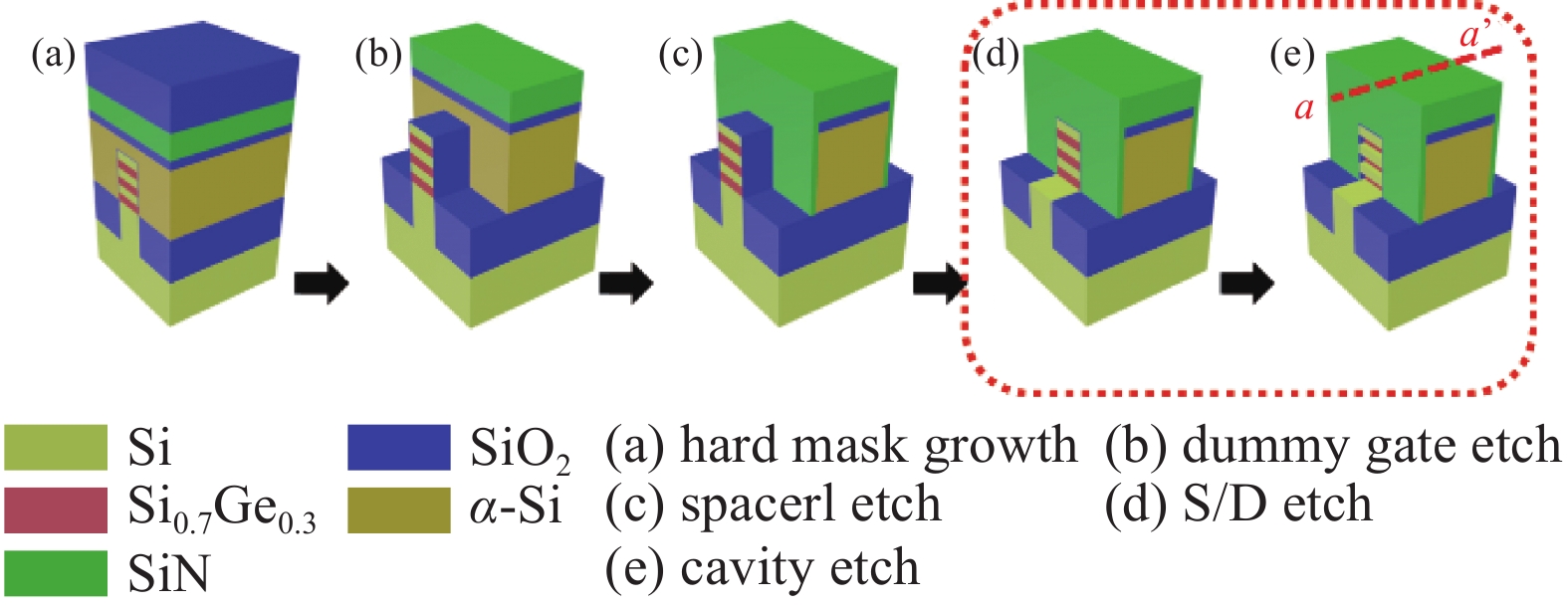

实验过程(如图1)所示。选用8英寸Si(100)衬底,在设备ASM E2000 plus中,通过减压化学气相沉积(Reduced pressure chemical vapor deposition,RPCVD)的方式外延生长Si0.7Ge0.3 (12 nm)/Si(18 nm)叠层。在形成Fin、浅槽沟道隔离(Shallow Trench Isolation,STI)和非晶硅工艺后,并沉积SiO2/SiN/SiO2完成硬掩膜图形化(如图1(a))。

本实验各向异性与各向同性刻蚀均在8英寸ICP刻蚀机Lam 9400 DFM上进行,通过光刻与刻蚀完成假栅图形化(如图1(b))之后,以假栅及侧墙自对准完成进行Si0.7Ge0.3/Si叠层的各向异性刻蚀挖除源漏区域Si0.7Ge0.3/Si叠层的图案(如图1(c)-(d))。在进行空腔蚀刻之前,湿法清洗去除钝化层,然后进入ICP刻蚀腔采用CF4/O2/He气体进行各向同性选择性蚀刻Si0.7Ge0.3(如图1(e))形成空腔,以确定内侧墙的生长位置和尺寸。

-

本实验采用CF4∶O2∶He=4∶1∶5的气体组合进行选择性各向同性SiGe刻蚀,静电卡盘的温度设置在80℃,ICP偏置射频(Bias RF)设置为零以最大程度降低离子的轰击能量以获得接近各向同性的刻蚀效果。具体的等离子反应式[16-17]如下:

在引入O2后会对SiGe以及Si NS表面氧化,同时因C与O结合易生成气态的CO或CO会在一定程度上增加CF4的F自由基的释放量。因为Ge是一种比Si更为活泼的元素[16],Ge的氧化也更容易被F基气体刻蚀,而SiO2是一种相对化学活性比较稳定的材料,在F基气体下需要一定的离子能量才会产生刻蚀,所以SiGe比SiO2更容易被F基气体刻蚀。He气作为惰性载气,具有使等离子分布更为均匀,降低刻蚀过程的微负载效应,降低刻蚀界面粗糙度的作用。

本文研究了SRF、气压、刻蚀时间以及刻蚀前清洗工艺对刻蚀结果的影响。样品的取样沿a-a’方向(如图1(e))得到沟道截面(如图2所示)进行SEM表征,观察不同条件下干法刻蚀的样品形貌并测量刻蚀深度以及形貌。

-

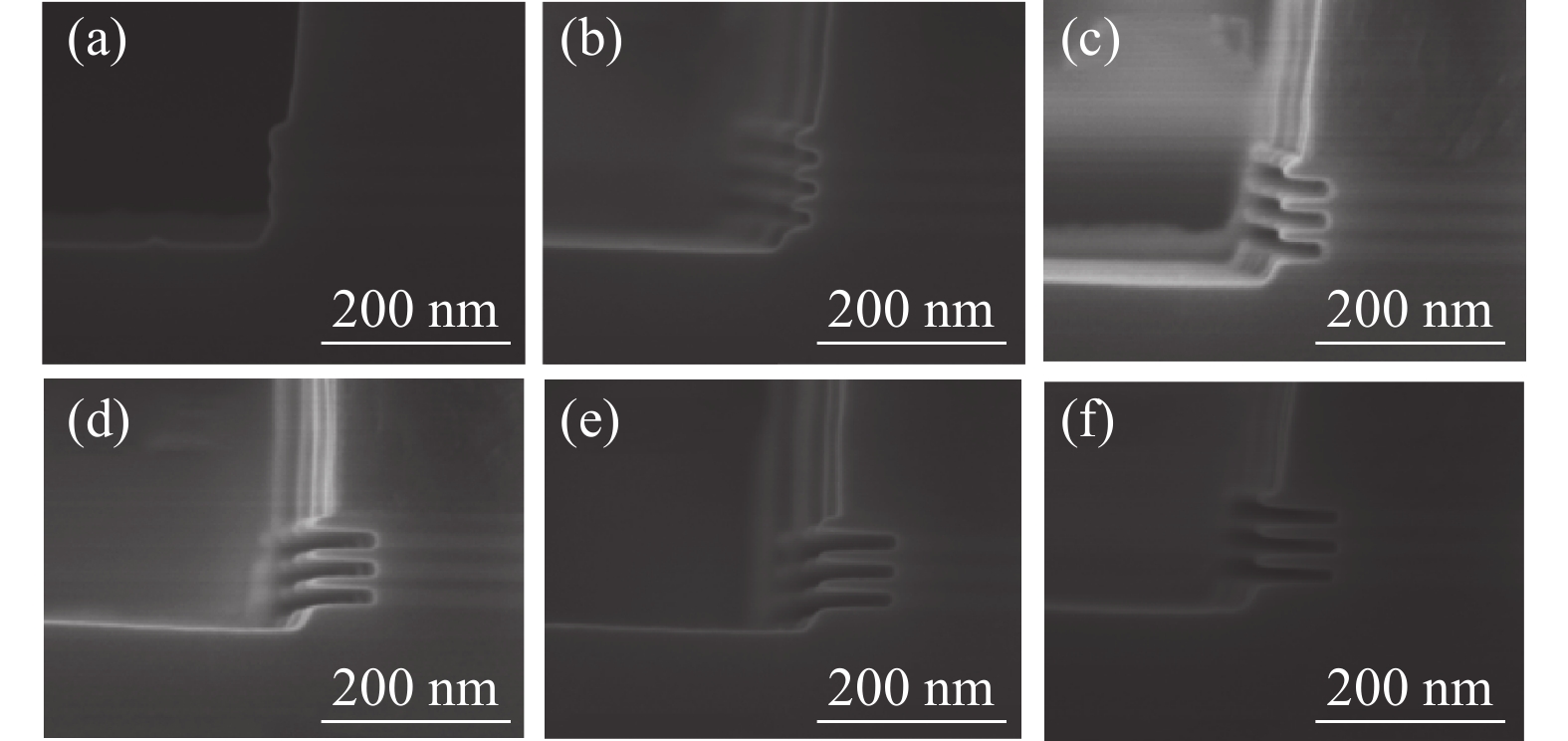

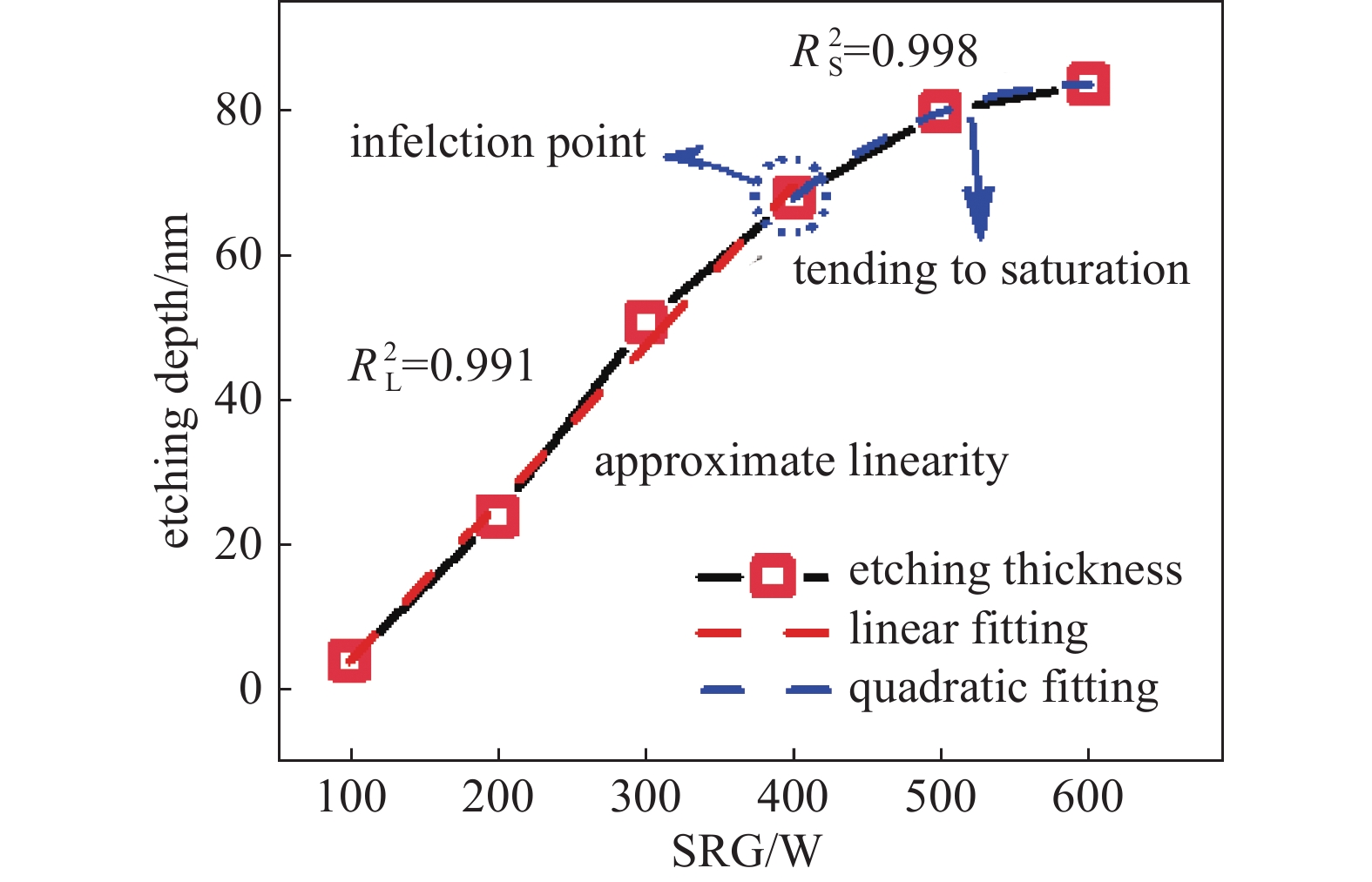

不同SRF下的刻蚀深度与形貌(如图3所示),固定刻蚀时间20 s,SRF设置为100、200、300、400、500、600 W的条件下,分别产生了3.86、23.77、50.48、67.68、79.53、83.27 nm的刻蚀深度。

在较低的SRF阶段(≤400 W),其线性拟合度为RL2=0.991,表明在此阶段,刻蚀深度随SRF的增大呈现接近一次函数的线性关系。在较高SRF阶段(>400 W),其二次函数拟合度为RS2=0.998,刻蚀深度逐渐趋于饱和(如图4)。这种趋势是因为低功率下气体解离度较低,随着SRF的增大,气体解离度呈现线性增大,导致参与反应的离子和自由基密度也呈现线性增大。当在拐点(本实验条件下大致为400 W)之后的较高功率时,是由于在气体流量的限制下,气体组合能转化的F自由基逐渐接近饱和,导致刻蚀深度增长趋于平缓。

-

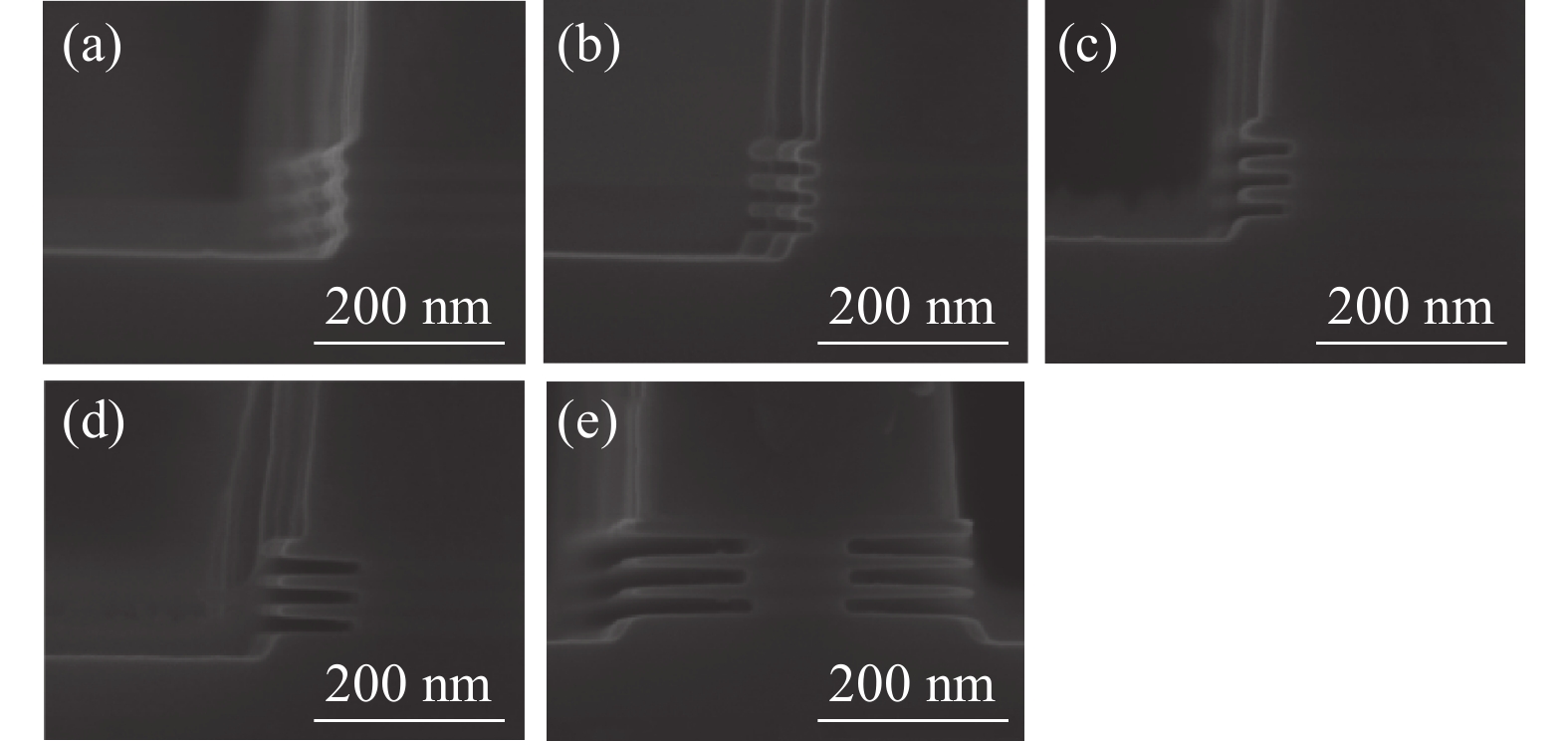

为了研究适合空腔刻蚀的气压,本节研究当中固定刻蚀时间为10 s,设置气压10、20、40、60、80 mT,分别得到7.21、18.91、51.6、79.23、136.67 nm的刻蚀深度(如图5所示)。

气压是等离子刻蚀中较为重要的参数,气压决定着等离子体中平均自由程和自由基的密度,由于在高压下的自由基密度增加,故产生更大的刻蚀深度,在进行二次函数拟合后得到的拟合度为0.987,这是由于在低气压下,能量较高,会使部分自由基离化。而在较高气压下,能量较小,自由基较为稳定,相比于低气压下有更高密度的自由基可以参与SiGe各项同性刻蚀,因此刻蚀深度可能并不呈现单一的线性增加,而是接近二次函数变化(如图6)。

从刻蚀形貌上看出20 mT的气压下获得了相对陡直的空腔刻蚀形貌(如图5(b)),是由于20 mT的气压下,等离子体的自由程相对较高且自由基密度适中,离子运动受侧壁的影响相对较小,所以获得了相对陡直的空腔刻蚀形貌,这样的条件下有利于对小尺寸的内侧墙进行精确空腔刻蚀控制。而在较高气压的情况下Si0.7Ge0.3牺牲层会产生“尖嘴状”存在部分Si0.7Ge0.3没有被刻蚀(如图6所示),这是因为等离子体自由程较低,受到上下纳米片的影响,进而会有部分Si0.7Ge0.3残留,表明高压的条件下,不利于内侧墙空腔结构的形成。

-

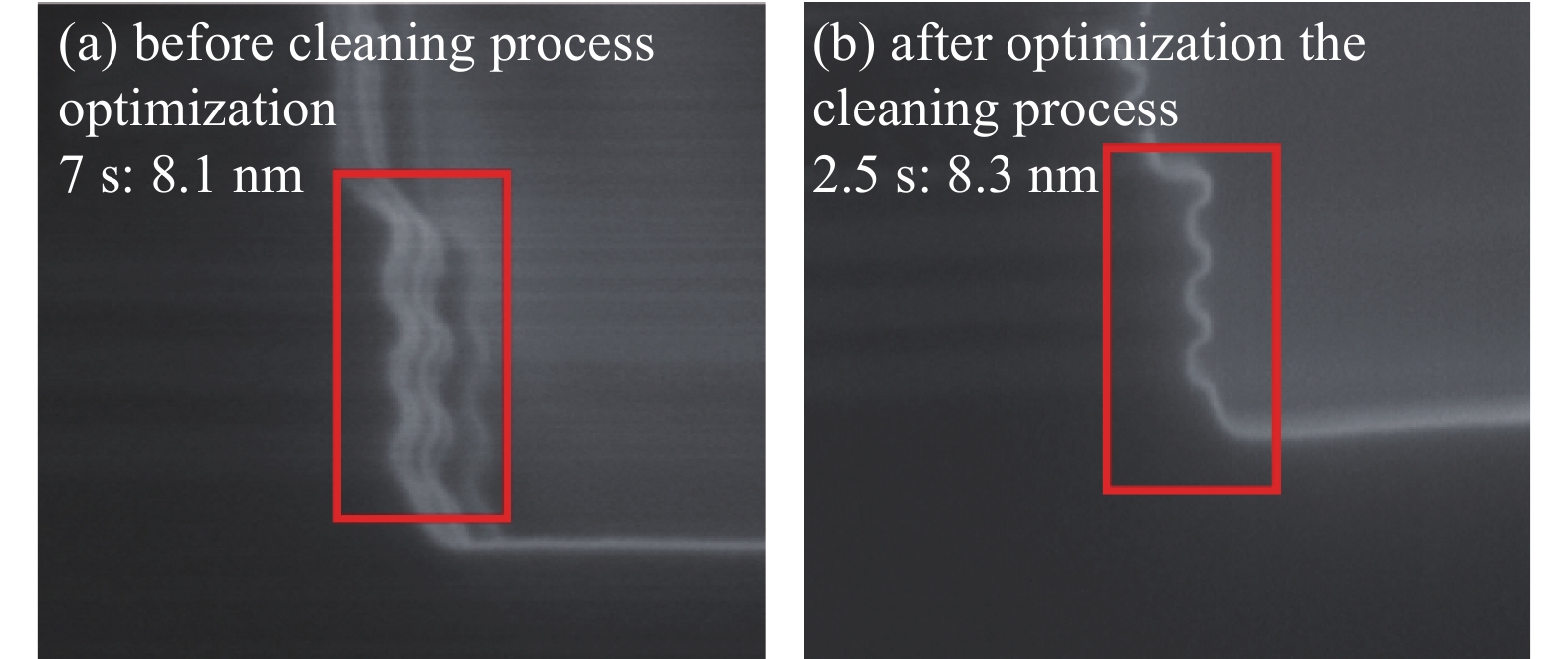

为了研究刻蚀前清洗工艺对空腔刻蚀形貌的影响,分别在刻蚀前进行单一DHF清洗与O3/DHF交替循环清洗进行实验对比,(如图7所示)可以明显观察到在O3/DHF交替循环清洗后,空腔刻蚀的轮廓接近矩形,要优于常规的清洗工艺后的轮廓。其原因可能是由于在各向异性刻蚀开叠层的过程中(如图1(d))的过程中,需要引入Br或C聚合物来保护侧壁,从而获得各向异性的陡直刻蚀形貌,以及侧壁形成后在空气中形成自然氧化层,单独依靠DHF很难彻底清洗掉聚合物保护层与自然氧化层,从而阻挡了干法刻蚀对SiGe的有效选择性刻蚀。而O3/DHF交替循环清洗中,O3将聚合物置换为氧化物,然后经过DHF溶液去除Si或SiGe的氧化物,从而达到钝化层(侧壁聚合物保护层与自然氧化层)较多去除的目的,使干法刻蚀剂更为有效选择性刻蚀SiGe。

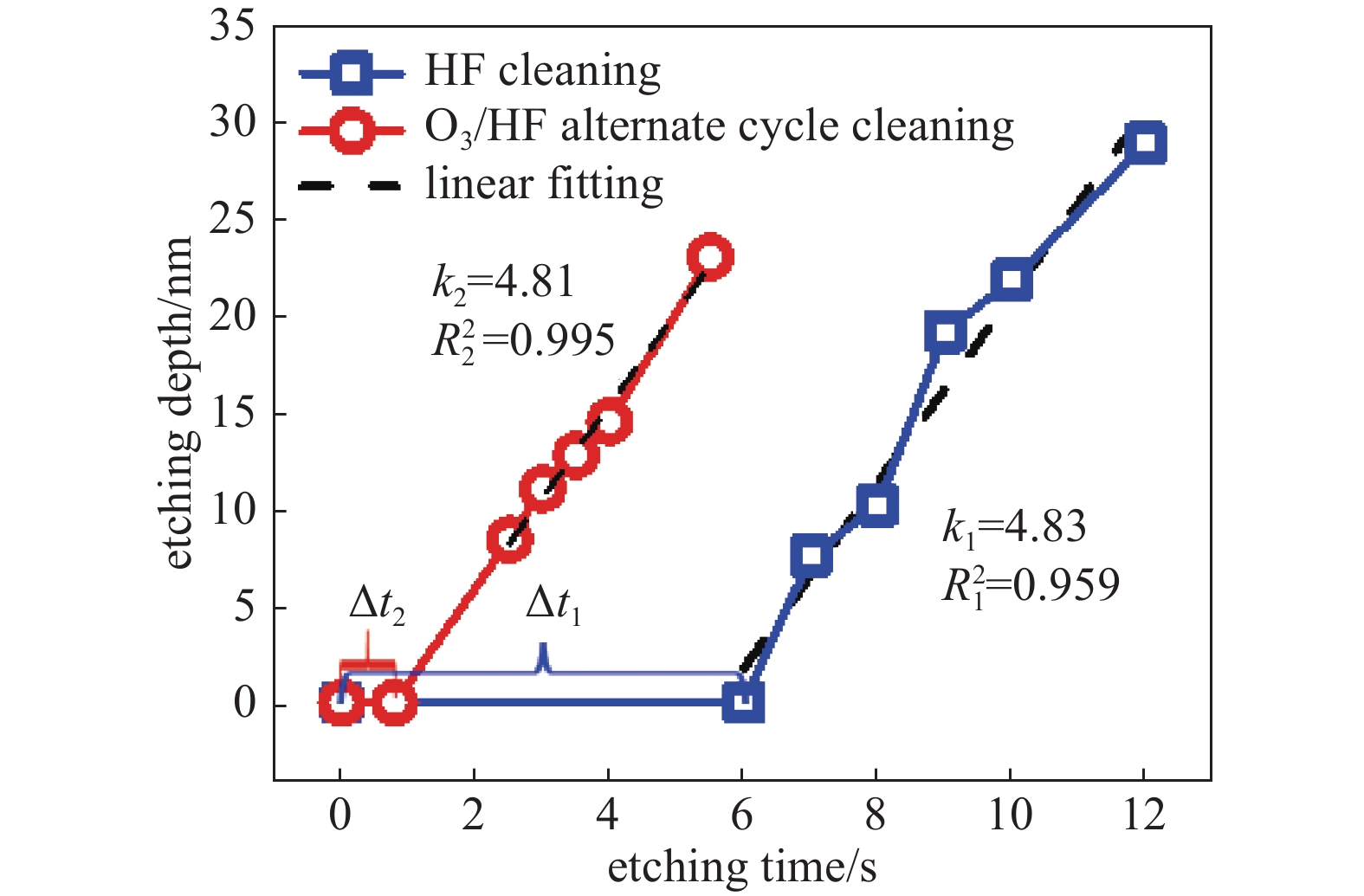

为了探究刻蚀前清洗工艺对空腔刻蚀深度的影响,在上述两种清洗工艺后,进行各向同性刻蚀实验对比,整个刻蚀过程可分为两个阶段:第一阶段即在∆

$ {t}_{1} $ 、∆$ {t}_{2} $ 时间段,需要刻蚀突破清洗后依然存在的钝化层(含清洗未彻底去除的钝化层以及清洗后进刻蚀腔前暴露大气的自然氧化层),此阶段并未对SiGe进行刻蚀,所以SiGe刻蚀速率为0 nm/s。第二阶段再进行SiGe刻蚀,SiGe刻蚀深度与时间之间存在较高的线性度(如图8)。故SiGe$ {D}_{E} $ 为刻蚀深度,$ k $ 为第二阶段SiGe刻蚀线性拟合的斜率也可认为是在第二阶段SiGe刻蚀平均速率。∆$ {t}_{1} $ 、∆$ {t}_{2} $ 分别为单一DHF清洗与采用O3/DHF交替循环清洗在第一阶段对钝化层进行刻蚀消耗所需时间;k1、k2分别是上述两实验中在第二阶段SiGe刻蚀线性拟合的斜率;R12、R22分别上述两实验中在第二阶段SiGe刻蚀线性拟合的线性度(如图8所示)。在两次实验当中得到

$ {k}_{1} $ 、$ {k}_{2} $ 分别为4.83、4.81,且线性度较高,即为两次实验在第二阶段SiGe刻蚀过程中平均速率近似相等。同时可观察到在O3/DHF交替循环清洗后比单一DHF清洗在更短的时间内($ \Delta {t}_{2} $ <$ \Delta {t}_{1} $ )进入第二阶段SiGe的刻蚀过程,这表明O3/DHF交替循环清洗工艺要比常单一DHF清洗具有更好的钝化层去除效果。 -

在空腔刻蚀的工艺中,理论上会造成对硅纳米片表面一定程度的损伤,体现为表面粗糙度增加,界面态密度增加,从而降低器件性能,因此对空腔刻蚀后Si NS的表面粗糙度的控制是很重要的[18-20]。为了直接表征界面微观状态,在固定的气体组合后,调整刻蚀时间、SRF、气压原子力显微镜(AFM)表征后得到Rq如表1所示。在相同的条件下刻蚀2.5、7、20 s (如图9所示),显示了通过AFM测量得到的Si NS粗糙度。结果表明,在此刻蚀条件下随着刻蚀时间的延长,粗糙度也会增大。在2.5 s刻蚀的表面粗糙度保持在较低的水平(Rq=0.101 nm)。

7种不同刻蚀样品的AFM表征得到Rq值(如表1),表明在高的SRF(样品3、4、5),长时间(样品1、2、6、5)刻蚀会使得Rq增大,是由于离子与自由基密度高或者长时间刻蚀,使蚀刻产物吸附在Si NS上,起到微掩蔽的作用,会导致非均匀刻蚀,从而增加表面粗糙度。而气压的增大(样品6、7)当中,粗糙度会有轻微的增大,表明在20 mT下,既有利于小尺寸刻蚀,又满足较低的Rq。

-

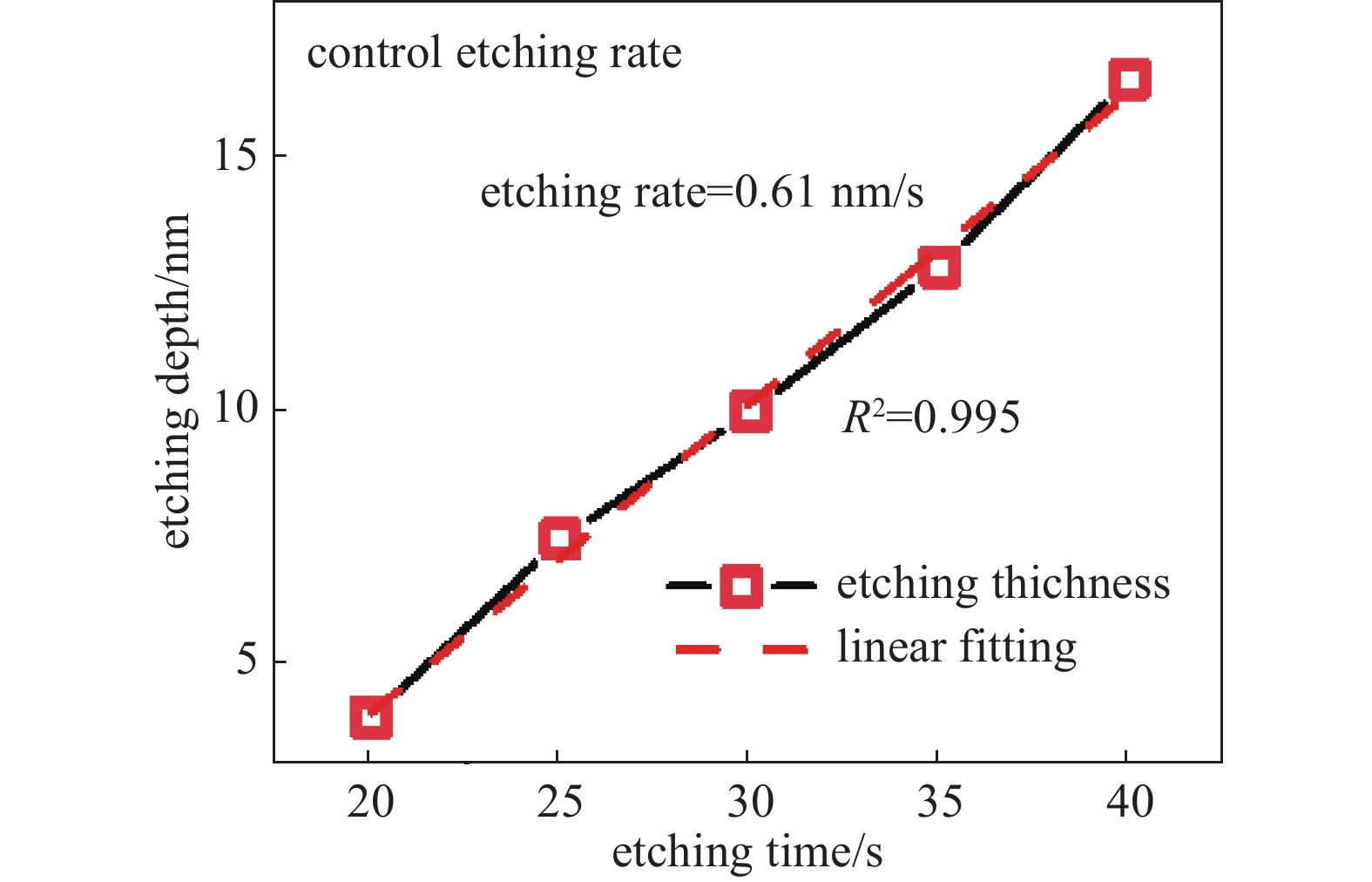

为了提高刻蚀精度,优化多种刻蚀参数的刻蚀条件下分别刻蚀20、25、30、35、40 s得到4、7.5、10、12.83、16.5 nm的刻蚀深度,第二阶段Si0.7Ge0.3平均刻蚀速率为0.61 nm/s,且线性度为R2=0.995(如图10所示),表明可通过调控多种刻蚀参数来实现高精度刻蚀结果。

-

由于空腔刻蚀“月牙”状将在后续的高k金属栅(High K Metal Gate,HKMG)填充之后会引起尖角异常放电,这将对器件的可靠性存在潜在的负面影响。故本文探索了一种可实现减弱“月牙”状的内侧墙空腔刻蚀工艺优化的方法。

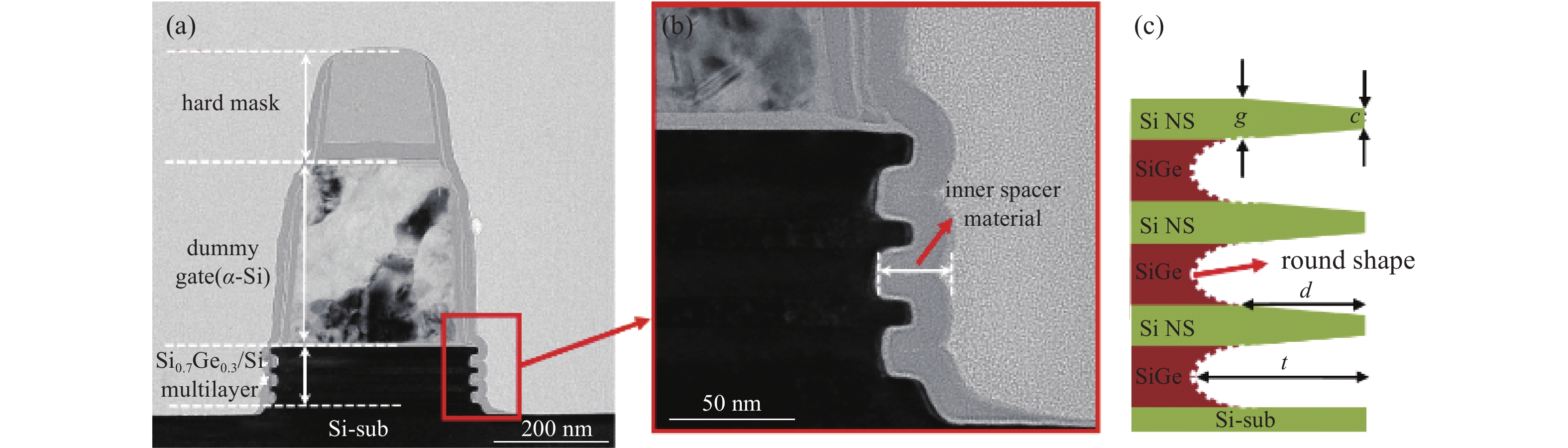

在经过多项刻蚀参数优化后,为了保持空腔 形貌,填充内侧墙材料后进行TEM表征(如图11所示)。O3/DHF交替循环清洗后,在3.5 s内产生13.9 nm的刻蚀深度,硅纳米片厚度为12 nm的内侧墙空腔,空腔轮廓的“月牙”状相对较小,矩形度为(d/t=11.6/13.93~83.3%)且低的硅损伤(e/g=9.9/11.7~84.62%)。“月牙”形貌得到改善,一方面状是由于钝化层得到彻底清除,另一方面因低气压下的粒子自由程相对较高,受侧壁的影响相对较小,刻蚀剖面速率一致性高,故刻蚀空腔轮廓较为陡直。进一步说明O3/DHF交替循环清洗相对单一的DHF清洗方案是一种更优的选择。

-

本文采用CF4/O2/He 混合气体在ICP刻蚀机上研究了SRF,气压及刻蚀前清洗工艺对各向同性干法刻蚀Si0.7Ge0.3的影响,获得了SRF影响刻蚀深度的线性区和准饱和区的,气压与刻蚀速深度呈现较强二次函数关系(实验区间内拟合度达到了0.987),采用优化后工艺,获得了较高的刻蚀Si0.7Ge0.3控制精度(0.61nm/s),较好的刻蚀轮廓(矩形度d/t~83.3%),较低的刻蚀界面粗糙度(Rq=0.101 nm),将为业界研制GAA 内侧墙模块提供主要的参考。

面向水平GAA内侧墙模块的干法Si0.7Ge0.3选择性刻蚀研究

Dry Selective Etching of Si0.7Ge0.3 for Horizontal GAA Inner Spacer Module

-

摘要: 针对环栅(Gate-All-Around,GAA) Si0.7Ge0.3的内侧墙(Inner spacer)空腔刻蚀难以精确控制尺寸和形貌的问题,本研究基于常规电感耦合等离子体(inductively coupled plasma,ICP)刻蚀设备,采用CF4/O2/He混合气体进行Si0.7Ge0.3干法各向同性选择性刻蚀实验,探究了包括激励射频源(source radio frequency,SRF)功率、气压、刻蚀前侧壁清洗工艺等因素对刻蚀结果的影响与机制。研究结果表明,SRF对刻蚀深度的影响是存在线性区与准饱和区的,气压与刻蚀深度在实验区间内呈二次函数关系,稀释的氢氟酸(Diluted HF,DHF)与O3交替清洗相对单一的DHF清洗方案在界面钝化层的去除与刻蚀形貌的控制上有更优的表现。经工艺方案优化,最终获得良好的工艺结果:刻蚀精度达到了0.61 nm/s,最优粗糙度Rq为0.101 nm,刻蚀轮廓矩形度高(d/t~83.3%)。本研究为内侧墙空腔刻蚀提供了一种解决方案。

-

关键词:

- Si0.7Ge0.3 /

- 空腔刻蚀 /

- 刻蚀精度 /

- 粗糙度 /

- 刻蚀形貌

Abstract: Aiming at the issue that it is difficult to accurately control the size and profile of the inner spacer cavity etching of Si0.7Ge0.3 in Gate-All-Around (GAA) process flow, based on the conventional inductively coupled plasma (ICP) etching tool, dry isotropic selective etching experiment of Si0.7Ge0.3 was carried out with CF4/O2/He mixed gas. The effects and mechanisms of factors such as the power of SRF (source radio frequency), gas pressure, and the sidewall cleaning process before etching were explored. The results show that there are linear and quasi-saturated regions in the effect of SRF on the etching rate, and there is a quadratic function relationship between gas pressure and etching rate in the experimental range. Diluted HF (DHF) and O3 alternate cycle cleaning process has a better performance than the single DHF cleaning in the removal of the interface passivation layer and the control of the etching profile. After the optimization of the process scheme, better process results are obtained: the etching accuracy reaches 0.61 nm/s, the optimal roughness Rq is 0.101 nm, and the rectangle of the etching profile is high (d/t~83.3%). This study provides a solution for the inner spacer cavity etching.-

Key words:

- Si0.7Ge0.3 /

- Cavity etching /

- Etching accuracy /

- Roughness /

- Cavity profile .

-

-

图 1 空腔刻蚀示意图。(a)Si 0.7Ge 0.3/Si 叠层和硬掩模生长;(b)光刻与刻蚀形成假栅;(c)spacer刻蚀;(d)源/漏刻蚀;(e)Si0.7Ge0.3各向同性选择性蚀刻形成空腔

Figure 1. Process flow of cavity etch. (a) Si0.7Ge0.3/Si Fin structure and hard mask growth, (b) lithography and etching patterning to form dummy gate, (c) spacer etching, (d) source/drain etching, (e) Si0.7Ge0.3 isotropic selective etching forms cavity

图 11 内侧墙空腔填充内侧墙材料后的TEM表征以及示意图。(a)整体TEM表征,(b)局部放大形貌TEM表征,(c)“月牙”状与硅损伤示意图

Figure 11. TEM characterization and schematic diagram of inner spacer cavity filled with material. (a) The overall TEM characterization, (b) the local magnified profile TEM characterization, (c) schematic diagram of round shape and silicon damage

表 1 不同刻蚀条件下的Rq

Table 1. The Rq value of different etching parameters

样品编号 SRF/W,气压/mT,时间/s Rq/nm 1 600,20,2.5 0.101 2 600,20,7 0.122 3 200,20,20 0.144 4 400,20,20 0.203 5 600,20,20 0.279 6 600,20,10 0.221 7 600,60,10 0.248 -

[1] Hisamoto D, Kaga T, Kawamoto Y, et al. A fully depleted lean-channel transistor (DELTA)-a novel vertical ultra-thin SOI MOSFET[C]. International Technical Digest on Electron Devices Meeting. IEEE, 1989, 833-836 [2] Natarajan S, Agostnelli M, Akbar S. A 14 nm logic technology featuring 2nd-generation finfet transistors, air-gapped interconnects, self-aligned doudle patterning and a 0.0588 um2 sram cell size[C]. International Electron Devices Meeting (IEDM), 2014, 71 [3] Cho H J, Oh H S, Nam K J, et al. Si FinFET based 10nm technology with multi Vt gate stack for low power and high performance applications[C]. 2016 IEEE Symposium on VLSI Technology. IEEE, 2016, 1-2 [4] Loubet N, Hook T, Montanini P, et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET[C]. 2017 Symposium on VLSI Technology. IEEE, 2017, T230-T231 [5] Radamson H H,Zhu H,Wu Z,et al. State of the art and future perspectives in advanced CMOS technology[J]. Nanomaterials,2020,10(8):1555 doi: 10.3390/nano10081555 [6] Li J,Li Y,Zhou N,et al. Study of silicon nitride inner spacer formation in process of gate-all-around nano-transistors[J]. Nanomaterials,2020,10(4):793 doi: 10.3390/nano10040793 [7] Holländer B,Buca D,Mantl S,et al. Wet Chemical Etching of Si, Si1− x Ge x, and Ge in HF: H2O2: CH3COOH[J]. Journal of The Electrochemical Society,2010,157(6):H643 doi: 10.1149/1.3382944 [8] Kil Y H,Yang J H,Kang S,et al. Selective chemical wet etching of Si0.8Ge0.2/Si multilayer[J]. JSTS:Journal of Semiconductor Technology and Science,2013,13(6):668−675 doi: 10.5573/JSTS.2013.13.6.668 [9] Cao Zhijun,Zhang Qingzhu,Wu Cinan,et al. Release of stacked nanowires for 5 nm CMOS Node: an experimental study[J]. Chinese Journal Vacuum Science and Technology,2018,38(2):121−126 (曹志军,张青竹,吴次南,等. 面向 5 nm CMOS 技术代堆叠纳米线释放工艺研究[J]. 真空科学与技术学报,2018,38(2):121−126(in chinese) doi: 10.13922/j.cnki.cjovst.2018.02.08 CAO zhijun, ZHANG Qingzhu, WU Cinan, et al. Release of Stacked Nanowires for 5 nm CMOS Node: An Experimental Study[J]. CHINESE JOURNAL VACUUM SCIENCE AND TECHNOLOGY, 2018, 38(2): 121-126 doi: 10.13922/j.cnki.cjovst.2018.02.08 [10] Hartmann J M,Destefanis V,Rabillé G,et al. HCl selective etching of SiGe versus Si in stacks grown on (1 1 0)[J]. Semiconductor science and technology,2010,25(10):105009 doi: 10.1088/0268-1242/25/10/105009 [11] Caubet V,Beylier C,Borel S,et al. Mechanisms of isotropic and selective etching between SiGe and Si[J]. Journal of Vacuum Science & Technology B:Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena,2006,24(6):2748−2754 [12] Donnelly V M,Kornblit A. Plasma etching: Yesterday, today, and tomorrow[J]. Journal of Vacuum Science & Technology A:Vacuum, Surfaces, and Films,2013,31(5):050825 [13] Loubet N, Kal S, Alix C, et al. A novel dry selective etch of SiGe for the enablement of high performance logic stacked gate-all-around nanosheet devices[C]. 2019 IEEE International Electron Devices Meeting (IEDM), 2019, 11.4. 1-11.4. 4 [14] Durfee C,Kal S,Pancharatnam S,et al. Highly Selective SiGe Dry Etch Process for the Enablement of Stacked Nanosheet Gate-All-Around Transistors[J]. ECS Transactions,2021,104(4):217 doi: 10.1149/10404.0217ecst [15] Li J,Wang W,Li Y,et al. Study of selective isotropic etching Si1−xGex in process of nanowire transistors[J]. Journal of Materials Science:Materials in Electronics,2020,31(1):134−143 doi: 10.1007/s10854-019-02269-x [16] Borel S,Arvet C,Bilde J,et al. Isotropic etching of SiGe alloys with high selectivity to similar materials[J]. Microelectronic engineering,2004,73:301−305 [17] Kumar A,Lee W H,Wang Y L. Optimizing the Isotropic Etching Nature and Etch Profile of Si, Ge and Si0.8Ge0.2 by Controlling CF4 Atmosphere with Ar and O2 Additives in ICP[J]. IEEE Transactions on Semiconductor Manufacturing,2021,34(2):177−184 doi: 10.1109/TSM.2021.3057100 [18] Lee H W,Choi Y,Shin D,et al. Epitaxial growth of a silicon capping layer to mitigate roughness after the selective chemical etching of Si1-xGex[J]. Thin Solid Films,2020,707:138048 doi: 10.1016/j.tsf.2020.138048 [19] Yin X,Zhu H,Zhao L,et al. Study of Isotropic and Si-Selective Quasi Atomic Layer Etching of Si1− xGex[J]. ECS Journal of Solid State Science and Technology,2020,9(3):034012 doi: 10.1149/2162-8777/ab80ae [20] Chang W Y, Chu C L, Luo G L, et al. Investigation on selectively etched SiGe and Si surface for Gate-All-Around CMOS devices fabrication[C]. 2022 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA). IEEE, 2022, 1-2 -

首页

首页 登录

登录 注册

注册

下载:

下载: